第3章 ハイエンドコンピューティング研究開発の動向

3.1 NEC DRP[4]

a)アーキテクチャ

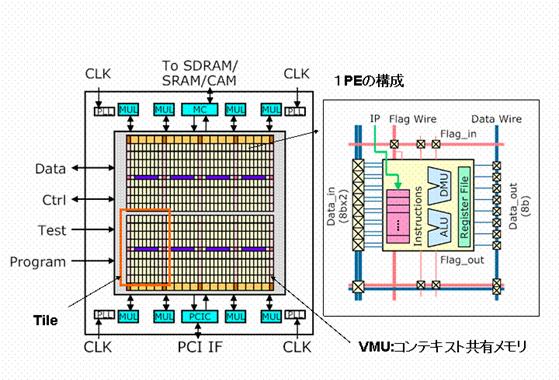

NECにより2002年に発表されたDRP(Dynamically Reconfigurable Processor)は、4X2のTileと呼ばれるreconfigurable unitから構成される。各Tileは図1に示す通り、8X8のPE(Processor Element)アレイ、状態制御を行なうシーケンサであるSTC(State Transition Controller)から構成される。また、8bitX256エントリのメモリ8セットを両側に持ち、これらを制御するメモリコントローラを2セット持つ。

各PEは8bitのALU, シフトやデータ制御、簡単な論理演算を行なうDMU(Data Management Unit)、8bitのFlip Flop、レジスタファイルから構成される。DRPは、上記構成のCoreの周辺部に32ビットの乗算器を8セット、メモリモジュール、PCIバスインタフェース、SDRAM/CAM/SDRAMインタフェースを搭載したシステムLSIとなっており、単独でPCIバスへの接続や外部メモリの制御が可能である。

DRPは、同社が1998年に開発したDRL同様、1クロックでコンテキスト切り替えが可能なマルチコンテキストデバイスで、Tile単位の部分再構成が可能である。一方で、DRLがLUT(Look Up Table)を構成要素とした細粒度のリコンフィギャブルデバイスであったのに比べ、DRPは8bitのPEを構成要素としたリコンフィギャブルなプロセッサである点が全く異なっている。

図1 DRP-1の構成

b)再構成

DRPは内部のメモリに最大16コンテキスト分の情報を蓄えることができ、最大で5コンテキストの中から次のコンテキストを選択し、動的に再構成をすることができる。次のコンテキストの選択はSTCに信号を送ることで行ない、動作を止めることなしに1クロックで行うことができる。

さらに、動作中に、コンテキスト切り替えの対象外のコンテキストに対してコンフィギュレーション ロードが可能である。この特徴により、仮想ハードウェアや動的適応ハードウェアの効率的な実現が可能となる。

これらの、コンテキスト切り替えや、Configuration dataロードは、Tile単位で行なうことができ、Tileごとに異なるコンテキスト構成を取ることができる。c)プログラム

C言語に制約を加えたCyber Cからの構成情報の生成が可能である。

3.2 IP Flex DNA Matrix[6]

a)アーキテクチャ

DNA Matrixは、IP Flex社が富士通と共に2002年に開発したチップで、32bitのALUが縦横のバスで接続された構造を持つ可変構造のプロセッサアレイである。デジタル家電向けとして新聞発表が行われたように、DNA Matrixは、制御用のRISCであるDAPと用途に応じて様々な形で組み合わせることで多様な応用が可能である。b)再構成

演算器間の接続はオンチップのConfiguration RAM上に格納され、1クロックで切り替えが可能である。c)プログラム

C言語およびMatlabのエントリがある。

3.3 PACT XPP[9]

a)アーキテクチャ

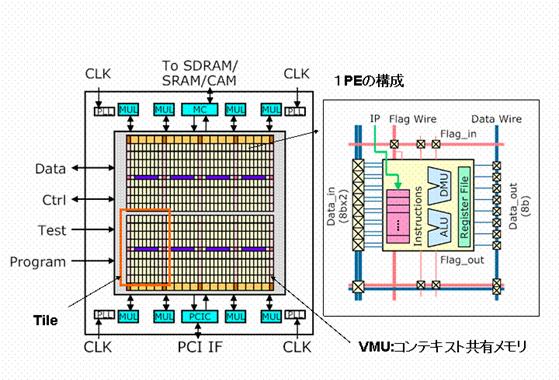

ドイツのPACT Informations technologieにより発表されたPACT XPP(eXtreme Processing Platform)は、階層的な構造を持つ再構成可能なプロセッサアレイである。図2に示すように、32bitのALU、FREG(Forward Register Object), BREG(Backward Register Object)から構成されるPAE(Processing Array Element)を2次元アレイ状に接続し、PAC(Processing Array Cluster)を構成する。このPACを複数接続することでシステムを構成する。バスの縦横の端には、I/Oが装備され、さらにConfiguration用RAMとマネージャがConfiguration busを介してConfiguration dataを流し込む。それぞれのアレイには互いに同期をとってパイプライン動作を容易に行なうことができる。

図2 PACT XPPの構成

b)再構成

Partial reconfigurationが可能である。また、一部を動作させながら、RAMより高速にConfiguration情報を流し込むことによりマイクロ秒オーダーで再構成が可能である。c)プログラム

上位レベルの記述エントリとしてXPP Cが開発されている。XPP Cは、標準Cのサブセットで、特殊なI/Oライブラリを用いる。記述は、XPP C Complierにより構造化されたHDLであるNML(Native Mapping Language)に変換される。このNMLを用いて直接記述を行なうことも可能である。

3.4 Quicksilver ACM[5]

a)構成

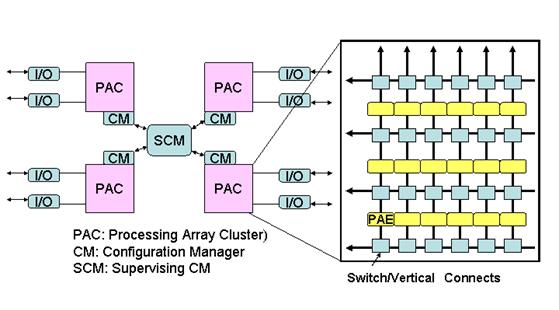

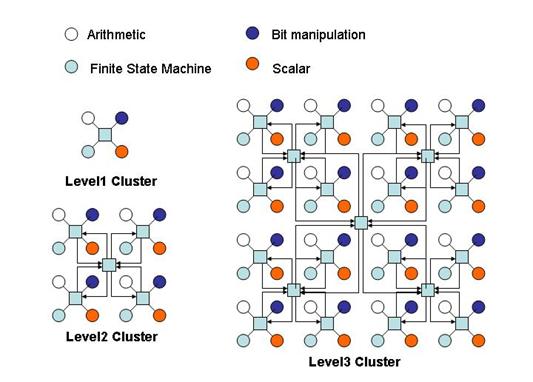

Quicksilver社から2002年に発表され、FPL2002の基調講演で発表が行なわれたが、詳細な情報が公開されていないので不明な点が多い。図3に示すように、算術計算用、ビット処理用、状態マシン、スカラープロセッサの4種類のプロセッサがクラスタを構成し、これらのクラスタを4つずつまとめて、階層型ツリー構造で接続される構造を持つ。

図3 Quicksilver ACMの構造

b)再構成

演算器間の接続はオンチップのConfiguration RAM上に格納され、1クロックで切り替えが可能である。c)プログラム

C言語でのプログラムが可能である。

3.5 CMU PipeRench[10]

a)アーキテクチャ

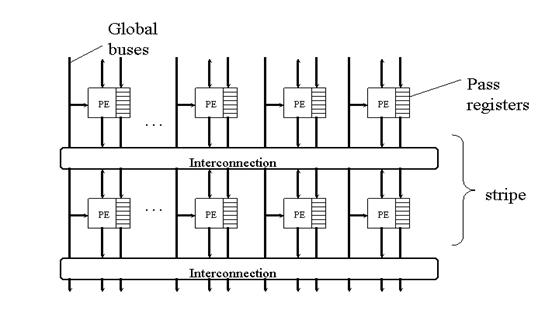

1997年からCMUで続けられているプロジェクトで2002年にチップが完成して話題となった。図4に示す、直線構造のパイプラインを基本とし、各Stripeには8bit構成のPEを16セット持つ。順にパイプラインを切り替えていくことで、仮想的に長大なパイプライン構造を実現することができる。b)再構成

Stripe単位に1クロックで構成を変更することが可能である。2002年に完成したチップは、チップ内に実Stripeを16保持し、これを切り替えるための仮想Stripeを256セット保持することができる。c)プログラム

ホスト上のAPIを用いて様々な環境からホストと協調動作する環境が作成されている。

図4 PipeRenchの構造

4. 粗粒度Reconfigurable Deviceの将来と問題点

粗粒度Reconfigurable Deviceの当面の応用分野はストリームデータを扱う通信における符号化、暗号化、復号化、音声、画像処理への応用が期待されており、実際にかなりの性能向上が実現されている[11][12]。

さらに、これらの粗粒度Reconfigurable Deviceは、要素プロセッサの機能と配線構造が可変なオンチップマルチプロセッサ、あるいは可変構造シストリックアレイとも考えられ、SIMD、データパラレル、VLSIアルゴリズムを容易に実装することができる。すなわち、いまやReconfigurable

Deviceとオンチップマルチプロセッサとの境界は限りなくアナログ的になりつつある。

また、動的再構成機能を利用することにより、今まで実現が困難であった仮想ハードウェア[13]の実現が期待される。

さらには、動的適応型ハードウェアの実現も可能である。動的適応型ハードウェアは、利用状況に応じて、自律的に動的に構成を変えることで、性能、電力消費を改善するハードウェアであり、その理想とする所は、設計者が細々とした指定をしなくても、状況に応じて、最適な構成にチューニングされていく。

一般的な再構成可能なデバイスでは構成の入れ替えに要する時間と電力消費が大きいため、動的再構成の利点が帳消しになってしまう場合が多い。しかし、DRPのように多数のコンテキストをチップ内で保持し、1クロックで入れ替えが可能であれば、チューニングのコストが小さいため、適応の効果が上回る場合が多くなる。筆者らはDRP上に動的適応型のスイッチを実現する研究を進めている[14]。

これは、到着するパケットが少ない場合、スイッチ中のクロスバが、より単純な構成に変更され、場合によっては配線のみになってしまうスイッチで、限定された条件で性能向上が確認されている。

一方で、ここで紹介した粗粒度Reconfigurable Deviceは粗粒度にしたが故の弱点を抱え込んでいる。すなわち、細粒度の要素から構成されるFPGA、CPLDと比べて、アプリケーションが演算器間のデータフロー上にうまく載らない場合、実現が極めて難しくなる点である。すなわち、今までReconfigurable

Systemが得意としたパターンマッチング、検索処理、短いデータ幅での特殊な演算処理の効率が悪化する可能性がある。これを防ぐためには制御処理を行なう部分と演算アレイから成るデータパスの組合わせを工夫した構成にする必要がある。

5. おわりに

この委員会の報告書も今年度で最後となるとのことだが、1998年から2001年までの報告書を読み返すと、かなり正確に現状が予測されていることがわかる。これらの報告書が示す通り、今後、Reconfigurable

Deviceは、VLSIアルゴリズムやマルチプロセッサアーキテクチャで培われた並列処理技術との組み合わせが重要になっていくであろう。

DRPを開発したNEC、DNAチップを開発したIP Flexおよび富士通、PCAを開発中のNTTなど、この分野での日本企業の貢献は大きく、研究面でも日本の大学、企業から、多くの業績が挙げられている。しかし、やはり本格的商用化の段階で米国ベンチャー企業の進出に押されつつあるのが現状である。

1998年の段階で、報告書で提言したように、国を中心とした大型プロジェクトが実行されていれば、状況はかなり違ったものになったであろう。この点既に機を逸した感があるが、この分野は、今後、アーキテクチャ、ソフトウェア、VLSIチップ、CAD等を巻き込んで大きく発展するだろう。

参考文献

[1] "Special Issue on Configurable System," IEEE Computer, April 2000.

[2] H.Amano, Y.Shiata: Reconfigurable Systems: New activities in Asia,"

Proc. on FPL2000 (LNCS1896), pp.585-595.[3] http://www.chameleonsystems.com/

[4] M. Motomura: ”A Dynamically Reconfigurable Processor Architecture,”

Microprocessor Forum, Oct. 2002.[5] http://www.qstech.com/

[6] http://www.ipflex.com

[7] 天野英晴: "直接解法マシン(Custom Computing Machines):

打倒プログラム格納型計算機への最後の希望,"

ペタフロップスマシン技術に関する調査研究II (日本情報処理開発協会

先端情報技術研究所編, 1998.[8] 天野英晴: "実用化が進むリコンフィギャブルコンピューティング,"

ハイエンドコンピューティング技術に関する調査研究II (日本情報処理開発協会

先端情報技術研究所編, 2001.[9] http://www.pactcorp.com

[10] http://www.ece.cmu.edu/research/piperench

[11] 山田ほか,“マルチコンテキストリコンフィギャブルデバイス上でのデータドリブン

アプリケーションの実装,” FPGA/PLD Conference and Exhibit. 2003.[12] 出口ほか,“DRPでのウェーブレットフィルタの実装,”信学報CPSY 2003年1月

[13] X.P.Ling, H.Amano:“WASMII:A Data Driven Computer on a Virtual Hardware,”

Proc. of FCCM pp33-42, 1993.[14] 天野:“マルチコンテキストデバイスを用いた動的適応型ハードウェアの提案,”

情処アーキテクチャ研報150-12、2002年11月