TM-1028

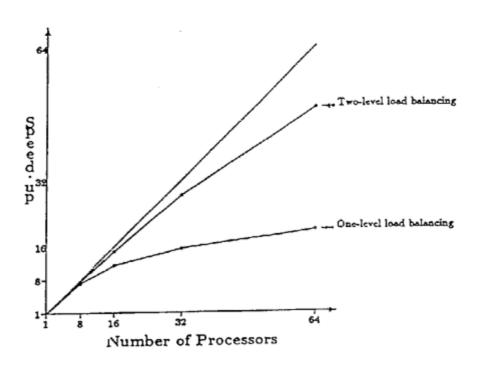

Second Joint ICOT/DTI-SERC Workshop on Decomposition of Parallel Applications and Benchmarking and Evaluation of Parallel Systems

> by S. Uchida

February, 1991

© 1991, ICOT

Mita Kokusai Bldg. 21F 4-28 Mita 1-Chome Minato-ku Tokyo 108 Japan (03)3456-3191 ~5 Telex ICOT J32964

# Second Joint ICOT/DTI-SERC Workshop on Decomposition of Parallel Applications and Benchmarking and Evaluation of Parallel Systems

Monday, October 15 ~ Wednesday, October 17, 1990 Shiba Park Hotel & ICOT Tokyo, Japan

Workshop Chairpersons: Dr. Paul Refenes (Dpt. of Trade & Industry)

Dr. Shunichi Uchida (ICOT)

Secretariat: Takashi Kurozumi (ICOT)

Hiroshi Hara (ICOT)

# Content

| l. Preface S. Uchida.                                              | P N Refere     |

|--------------------------------------------------------------------|----------------|

| 2. Details of the Workshop (Schedule and Participants)             | I. IV. Italica |

| 3. Presentations                                                   |                |

| 3-1 Overview of the Final Stage R&D of FGCS Project                | S. Uchid.      |

| 3-2 Overview of Parallel Computing Research in the UK              |                |

| and Europe                                                         | P. N. Refene   |

| 3 3 PIM Architectures and R&D Status                               |                |

| 3-4 Evaluation of the KL1 Implementation on the Multi-PSI          |                |

|                                                                    |                |

| 3-5 Benchmarking and Evaluation of Software Systems the EDS        |                |

| and Flagship Project                                               | . P. Townsend  |

| ***************************************                            |                |

| ***************************************                            |                |

| 3-6 Performance Aspects of the EDS Parallel Processing Machine     |                |

| ***************************************                            | S. J. Cockroft |

| ***************************************                            |                |

| 3-7 Research on parallel Inference Systems in the Fifth Generation |                |

| Computer Systems Project                                           | T. Chikayama   |

| 3-8 KL1 Programming environment-PIMOS                              |                |

| 3-9 Progress in the Development of th Date Diffusion Machine       |                |

| D.                                                                 | H. D. Warren   |

| 3-10 A Programming Environment for Parallel MIMD Machines          |                |

| 3-11 Decomposition of Parallel Applications for SIMD Machines      |                |

| 3-12 Parallel Application Program Research at ICOT                 |                |

| 3-13 MGTP: A Hyper-matching Model-Generation Theorem Prover        | ,,             |

| with Ramified Stacks                                               | R. Hasegawa    |

| 3-14 Parallel Programming in LSI CAD Systems                       |                |

| 3-15 Parallel Programing in Genome Analysis System                 |                |

| 3-16 Constra | int Logic Programming and Its I   | Parallel Implementation:     |

|--------------|-----------------------------------|------------------------------|

| Guardeo      | l Definite Clauses with Constrain | nts D. Hawley                |

|              |                                   | A. Aiba                      |

| 3-17 Mappin  | g Applications onto Various Para  | allel Architectures          |

| using Fi     | ecntional Language and Program    | Transformation J. Darlington |

| 3-18 Panel d | iscussion                         | K. Furukawa                  |

|              |                                   | D. H. D. Warren              |

|              |                                   | J. Darlington                |

|              |                                   | T. Chikayama                 |

|              |                                   | N. Ichiyoshi                 |

|              |                                   |                              |

# 4. Guide to the Japan and UK Demonstrations

- 4-1 Japanese Demonstrations

- 4-2 UK Demonstration

### Preface

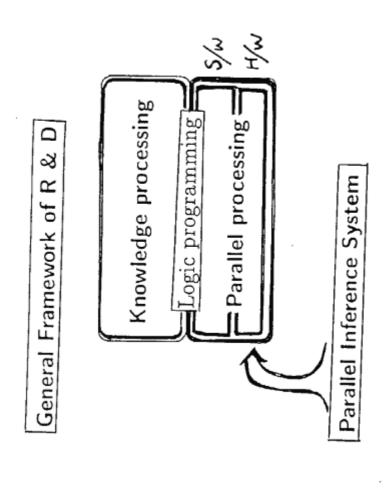

It has been eight years since the Fifth Generation Computer Systems Project started. The main aim of the project was to develop new computer technologies for knowledge information processing unifying "knowledge processing" technology and "parallel processing" technology using logic programming.

It was several years before the start of the project that researchers of U.K. and Japan realized the importance of logic programming as a link between these two technologies. Since then, researchers in both countries have been exploring the new research field of logic programming in co-operation with each other.

In these eight years, a great deal of research effort has been made toward the goal of FGCS throughout the world and produced many excellent results. The Second Joint ICOT/DTI+SERC Workshop is the evidence of this progress and of international co-operation. Through the presentations and discussions made in this workshop, we are sure that the researchers could convince themselves of the appropriateness of their research direction and sharpen the focus for the future.

These proceedings consist of papers and lecture notes that can be divided into four groups. First, there are overviews of the final stages of the FCCS project, and of Parallel Computing Research in Europe and the U.K. These overviews summarize progress in the areas of Architecture, Operating Systems and application.

Second, there are papers on the topic of Benchmarking and evaluation of parallel systems. These papers describe both benchmaking strategy and specific benchmarking examples from ICOT.

Third, there are papers dealing with the problem of Decomposition and mapping of parallel applications. These papers describe methods and techniques for decomposing and mapping applications to architectures. They also describe software tools.

Fourth, there are papers describing the demonstrations done by both Japan and U.K. sides. These papers introduce what kind of problems can actually be handled by the current technology.

It is our sincere hope that the workshop proceedings and lecture notes will serve as a valuable reference service for the researchers being engaged in the parallel processing and knowledge processing in both countries for years to come.

Finally, we would like to thank you the many people from U.K. and ICOT who provided high quality input to the proceedings and the discussion sessions.

> Shunichi Uchida Research Department ICOT

Paul Refenes Information Technology Directorate DTI

# Second Joint ICOT/DTI-SERC Workshop

# 1 Date and Place

Oct. 15 (Mon) Shiba Park Hotel Oct. 16 (Tue) ICOT Annex Oct. 17 (Wed) ICOT Annex

# 2 Topics of the workshop

- Decomposition of parallel applications

- 2) Benchmarking and evaluation of parallel systems

# 3 Participants and their presentations

1) UK side

D.H.D. Warren (U. Bristol): Progress in the Development

of the Data Diffusion Machine

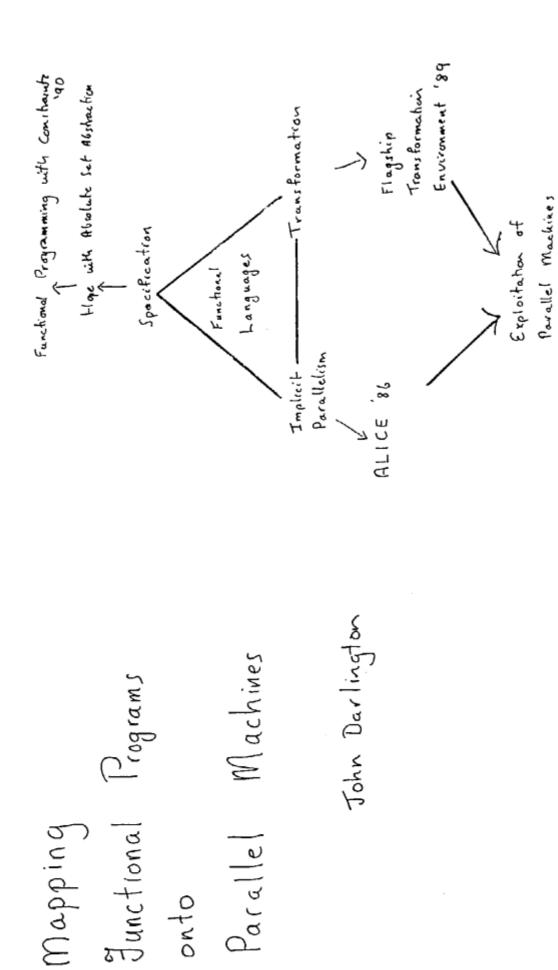

J. Darlington (Imperial C.): Mapping Application onto Various Parallel

Architectures using Functional Language and

Program Transformation

P. Refenes(DTI): Overview of Parallel Computing Research

in the UK and Europe

P. Evans (MEIKO): A Programming Environment for Parallel MIMD Machines

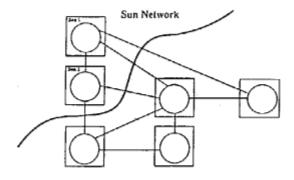

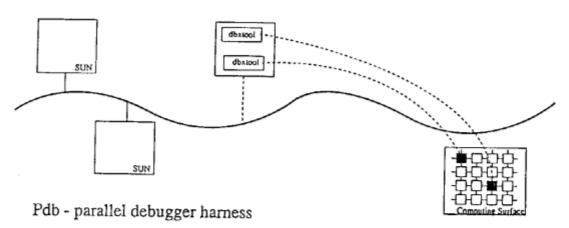

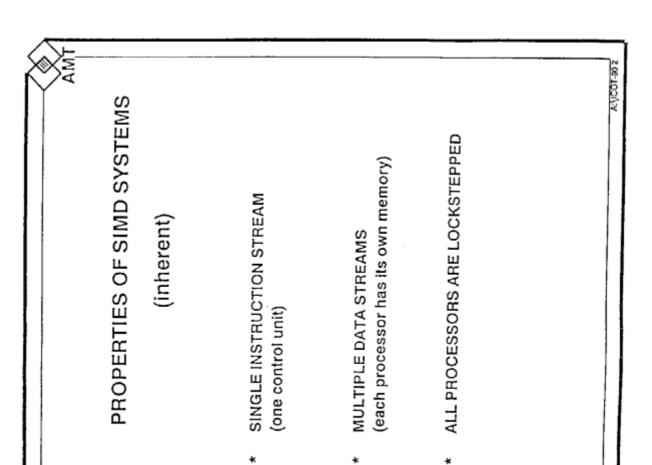

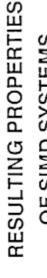

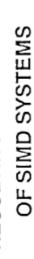

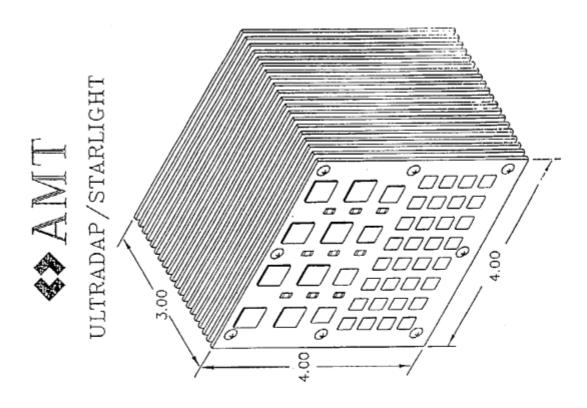

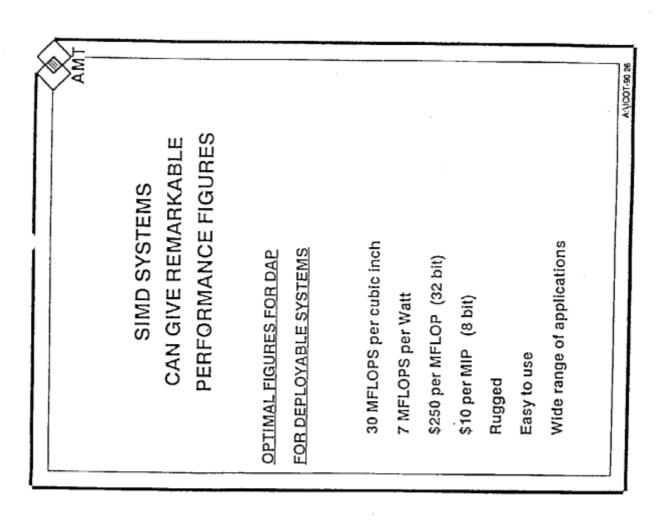

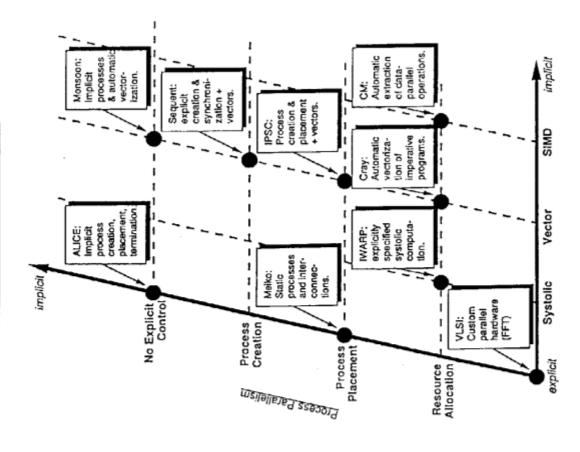

G. Manning (AMT): Decomposition of Parallel Applications for SIMD Machines

P. Townsend (ICL): Benchmarking and Evaluation of Software Systems

- the EDS and Flagship Projects

C. Hughes(LOGICA)

D. Watson(PARSYS)

C. Sharpington(Thorn-EMI)

# 2) Japan side

H. Tanaka (U.Tokyo): Welcome

K. Hirata (ICOT-1L): PIM Architectures and R&D Status

Y. Inamura (ICOT-1L) and K. Nakajima (Mitsubishi): Evaluation

of the KL1 Implementation on the Multi-PSI

T. Chikayama (ICOT-2L): Research on Parallel Inference Systems

in the FGCS Project

H. Yashiro (ICOT-2L): KL1 Programming Environment - PIMOS -

N. Ichiyoshi (ICOT-7L): Parallel Application Program Research at ICOT

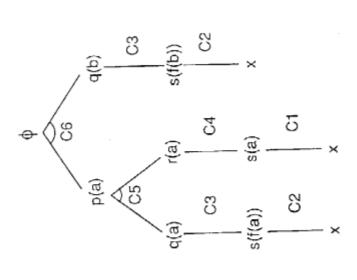

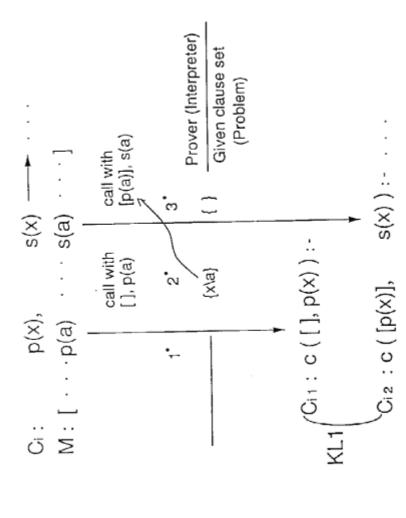

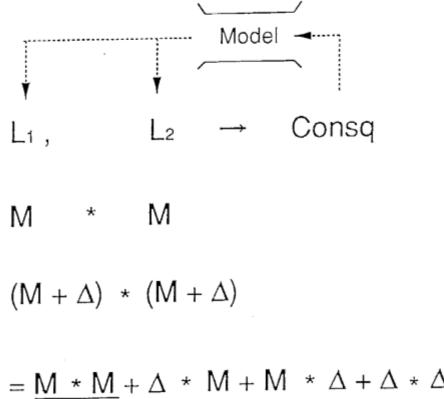

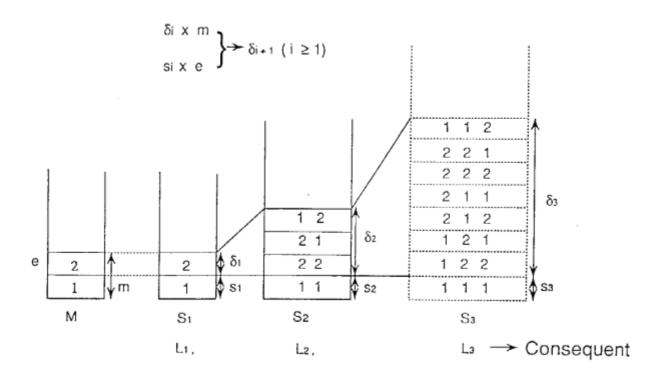

R. Hasegawa (ICOT-5L): MGTP: A Hyper-matching Model-Generation

Theorem Prover with Ramified Stacks

D. Hawley and Λ. Aiba (ICOT-4L):

Constraint Logic Programming and Its Parallel Implementation:

Guarded Definite Clauses with Constraints

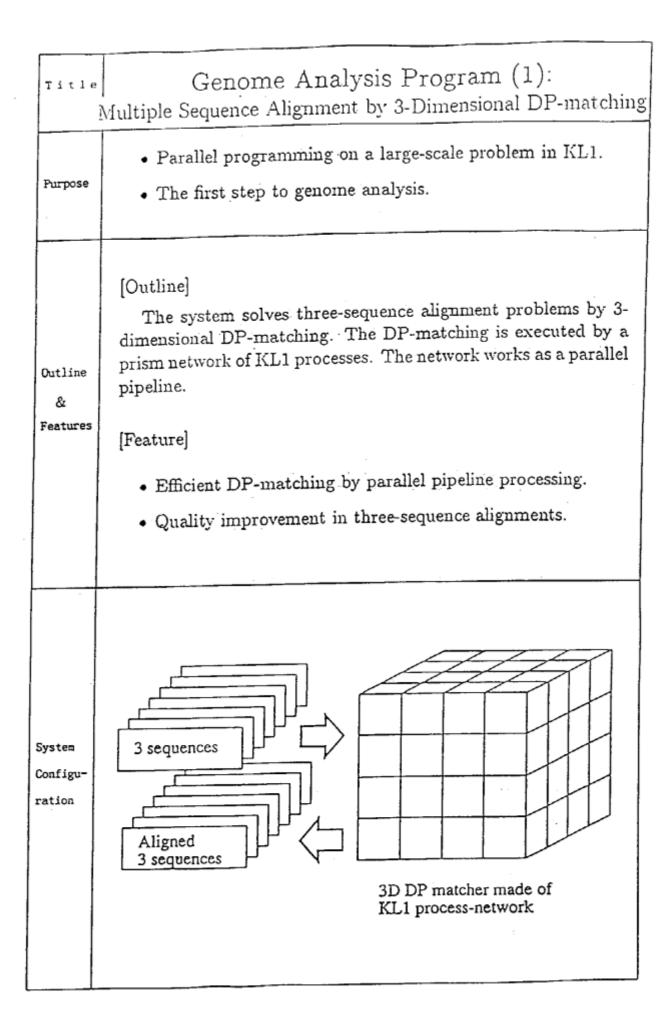

K. Nitta (ICOT-7L): Parallel Programming in Genome Analysis System

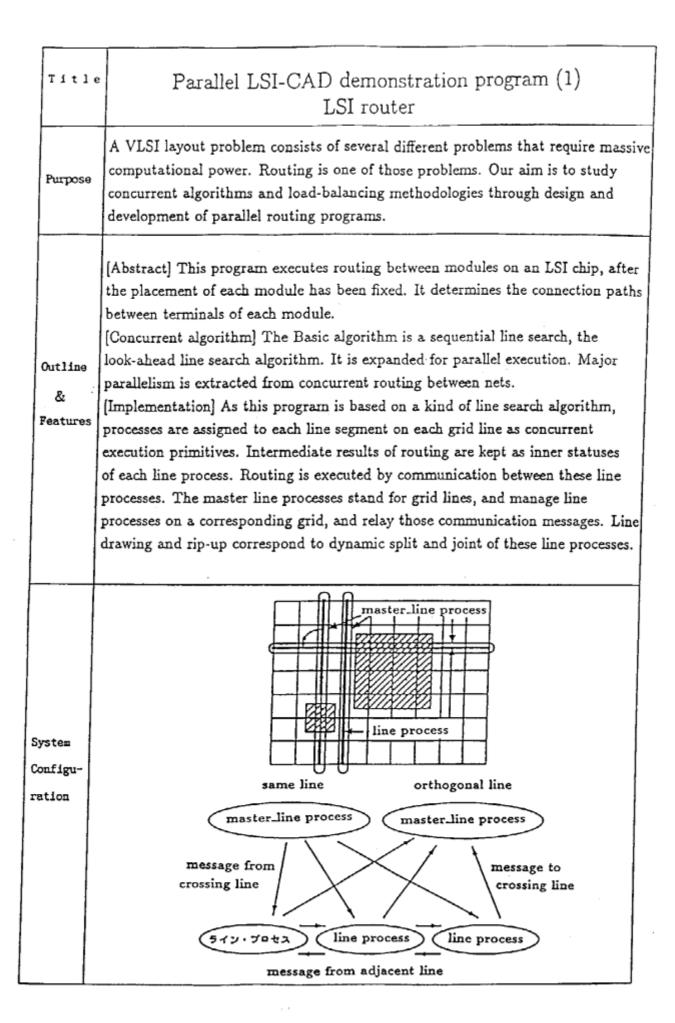

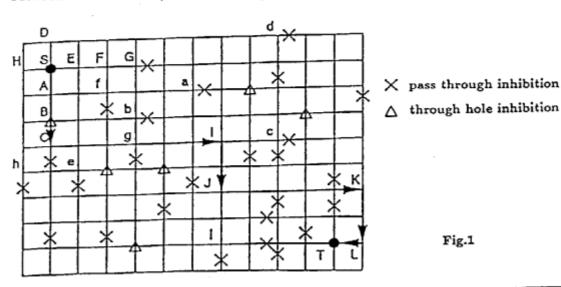

K. Taki (ICOT-7L): Parallel Programming in VLSI CAD Systems

A. Goto (NTT)

S. Uchida (ICOT): Overview of the Final Stage R&D of FGCS Project

K. Furukawa (ICOT)

K. Fuchi (ICOT)

and a few more researchers from ICOT and manufacturers

# 4 ICOT demonstration (3rd day afternoon)

# 4.1 Parallel systems

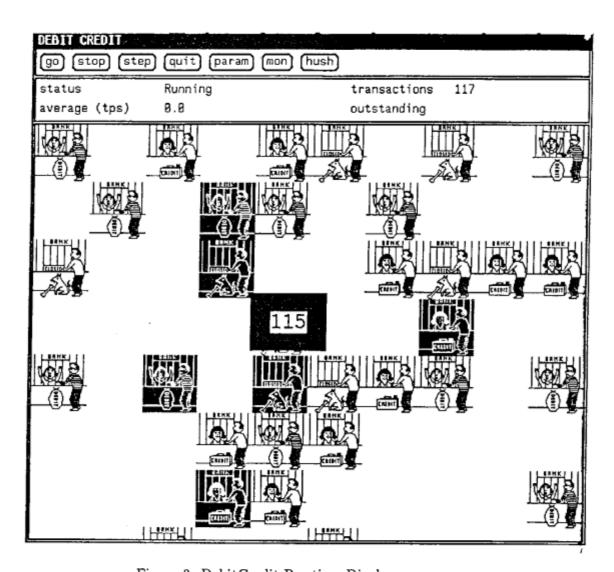

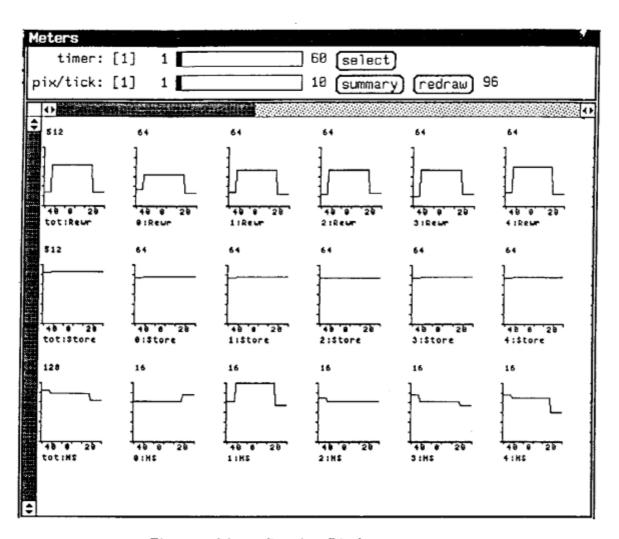

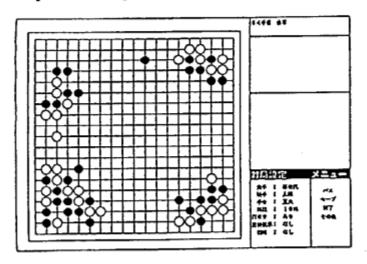

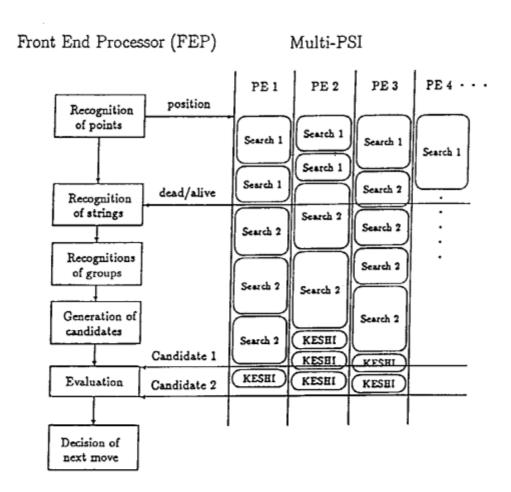

(Written in KL1 and running on the Multi-PSI/PIMOS)

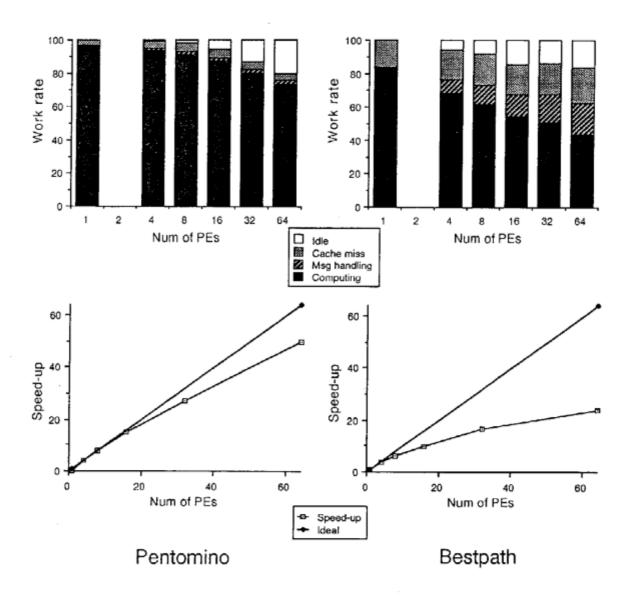

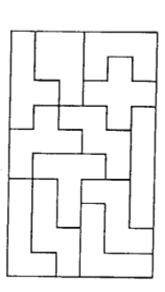

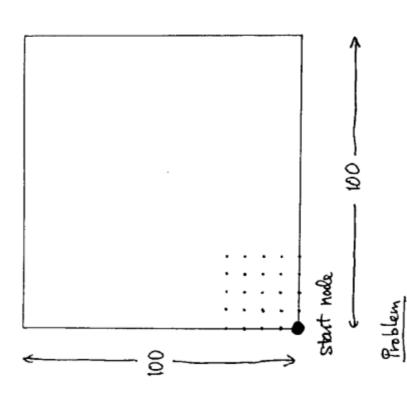

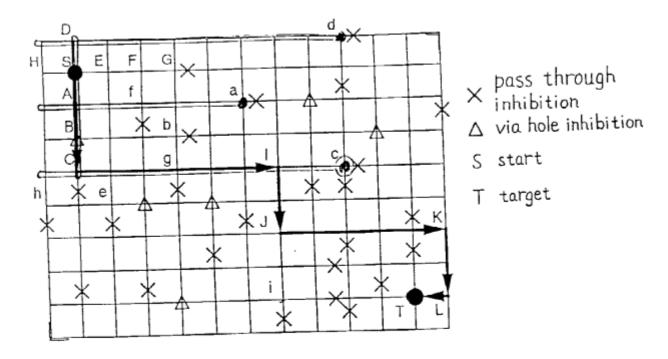

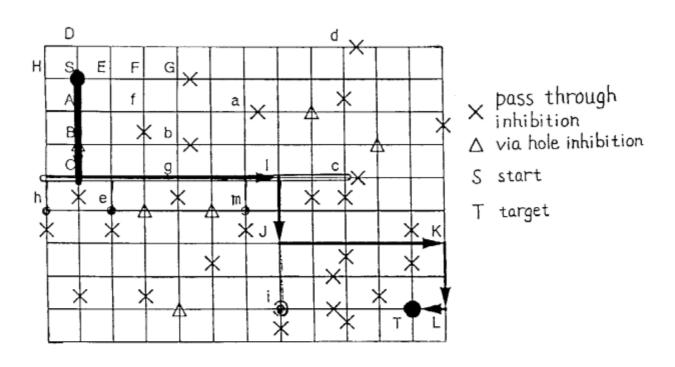

- Small benchmarking programs (Pentomino, Bestpath)

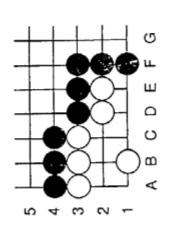

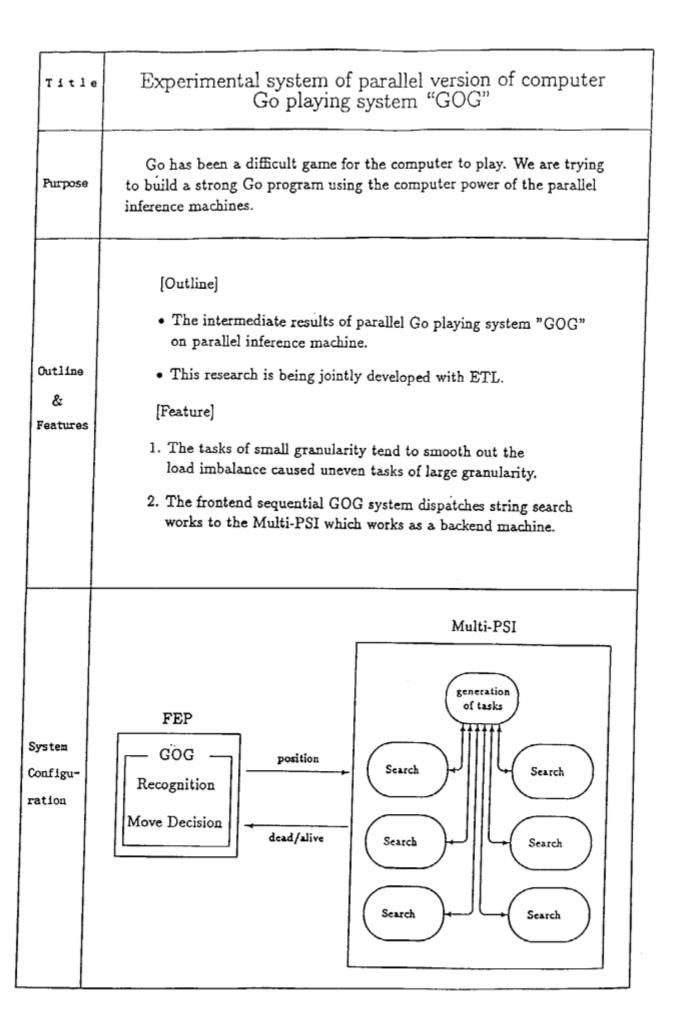

- Go-playing program: GOG

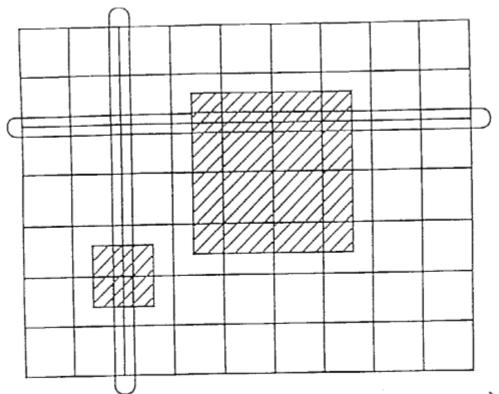

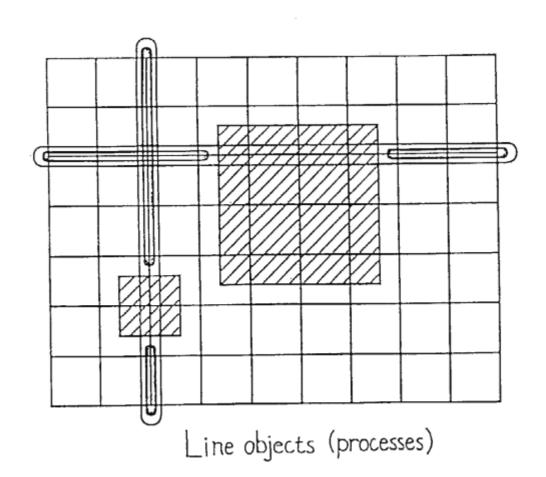

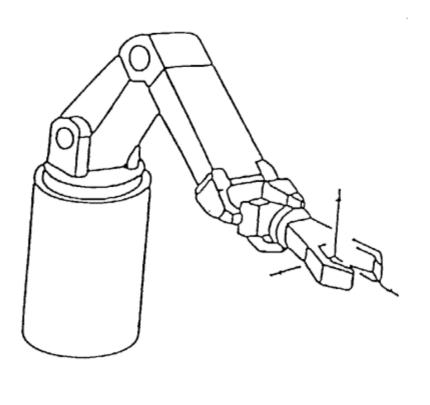

- LSI CAD programs (Logic simulation and Routing)

- Legal reasoning program

- Genome analysis programs

# 4.2 Sequential systems

(Written in ESP and running on the PSI/SIMPOS)

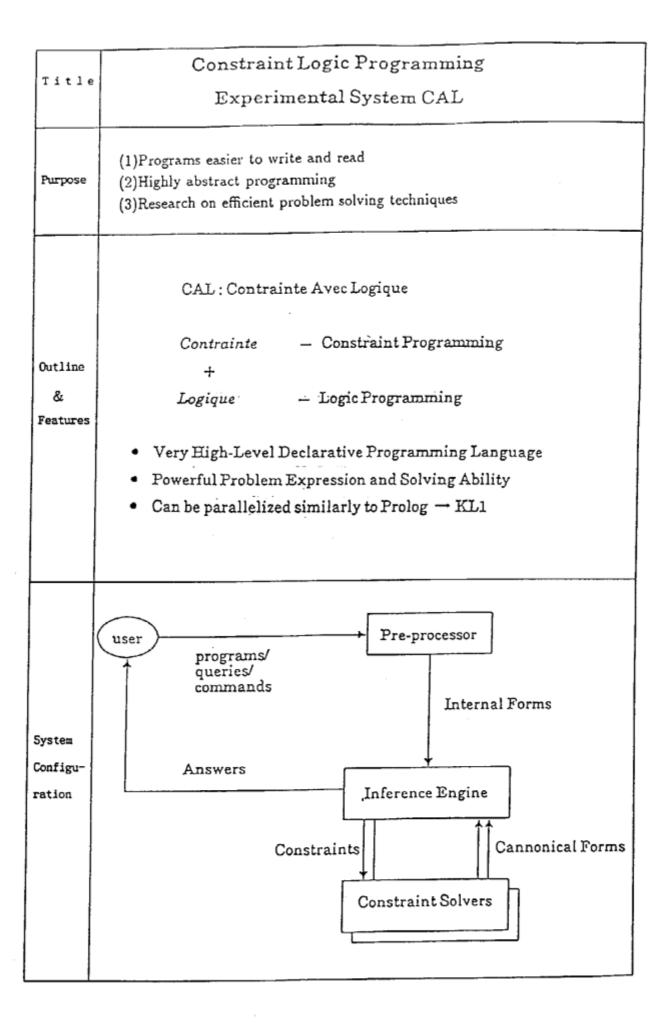

- Constraint logic programming language: CAL

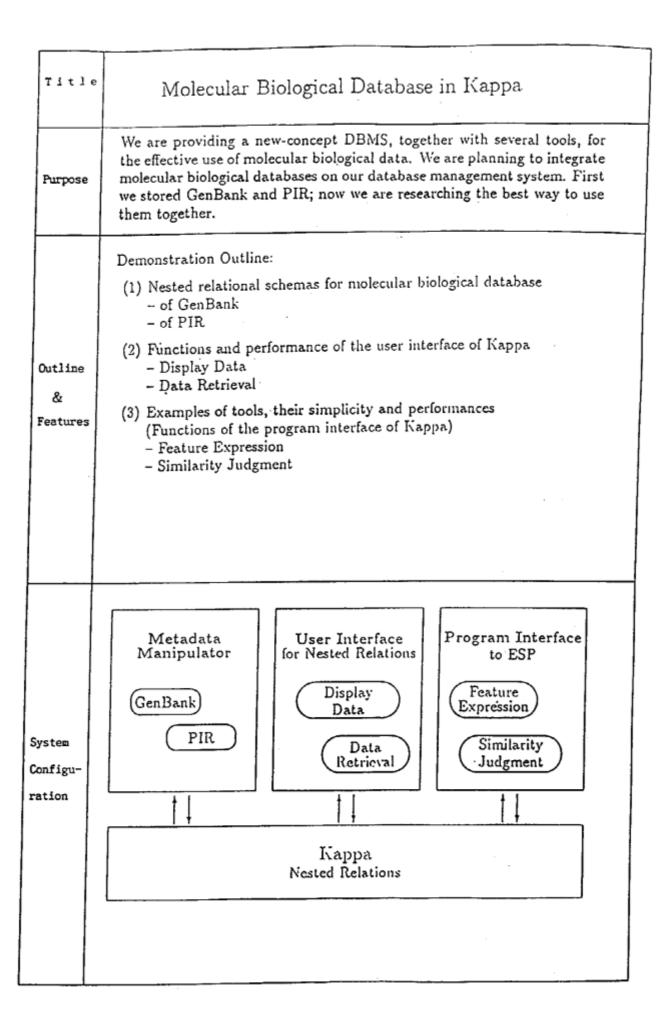

- Molecular biological database in Kappa

### Time table 5

# Second Joint ICOT/DTI-SERC Workshop (Tokyo, Oct.15-17, 1990)

|                                  | 10/15 (Monday)            | 10/16 (Tuesday)      | 10/17 (Wednesday)                          |

|----------------------------------|---------------------------|----------------------|--------------------------------------------|

| 9:30                             | @ Shiba Park Hotel        | @ ICOT Annex         |                                            |

| 10:00<br>10:10                   | Tanaka:Welcome (10)       | Warren (50)          | Darlington (50)                            |

| 10:20<br>10:30                   | Uchida (40)               | Evans (40)           | Break (10)                                 |

| 10:50<br>11:00<br>11:20<br>11:30 | Refenes (40)              | Break (20)           | Mini Panel (90):<br>Darlington,<br>Warren, |

|                                  | Break (20)                | Manning (40)         | Furukawa,<br>Chikayama                     |

| 11:50<br>12:00                   | Hirata (40)               |                      |                                            |

| 12:30                            |                           | Lunch                |                                            |

| 13:30                            |                           |                      |                                            |

|                                  |                           | Ichiyoshi (40)       |                                            |

| 14:00<br>14:10                   | Inamura/<br>Nakajima (40) | Hasegawa (40)        |                                            |

| 14:40<br>14:50                   | Townsend (50)             | Coffee Break (30)    |                                            |

| 15:20<br>15:30                   | Coffce Break (30)         | Taki (50)            | ICOT Demonstrations (Yoshioka)             |

| 16:00<br>16:10                   | Chikayama (50)            | Nitta (40)           |                                            |

| 16:50                            | Yashiro (40)              | Hawley/<br>Aiba (40) |                                            |

| 17:30<br>17:50                   |                           |                      |                                            |

| 18:30                            | Reception                 |                      | Farewell Party                             |

|                                  | @Shiba Park Hotel         |                      | @"Chugoku Hanten"                          |

# 6 Participants

# [ British Participants ]

| Name                 | Organization             | Department  | Position             |

|----------------------|--------------------------|-------------|----------------------|

| Academia             |                          |             |                      |

| Dr John Darlington   | Imperial College         | Computing   | Professor            |

| Dr David H.D. Warren | Bristol University       | Computing   | Professor            |

| Government           |                          |             |                      |

| Dr Paul Refenes      | Department of Trade      | Information | Consultant           |

|                      | & Industry               | Technology  |                      |

|                      | -                        | Directorate |                      |

| Industry             |                          |             |                      |

| Dr Geoff Manning     | Active Memory Technology | Board       | Managing Director    |

| Dr Patrick Evans     | MEIKO                    |             | Saftware Engineering |

|                      |                          |             | Manager              |

| Dr David Watson      | PARSYS                   | Board       | Managing Director    |

| Dr Paul Townsend     | ICL-Manchester           |             | Parallel Systems     |

|                      |                          |             | Manager              |

| Mr C. Sharpington    | Thorn-EMI                |             |                      |

| Dr Clifton Hughes    | LOGICA                   |             | Principal Consultant |

# [ Japanese Participants ]

|                       | 1            |                |                      |

|-----------------------|--------------|----------------|----------------------|

| Name                  | Organization | Department     | Position             |

| Dr Hidehiko Tanaka    | U of Tokyo   | Electrical Eng | . Professor          |

| Dr Hanpei Koike       | U of Tokyo   | Electrical Eng |                      |

| Dr Atsuhiro Goto      | NTT          | Software Lab   | Senior Researcher    |

| Mr Rikio Onai         | NTT          | Software Lab   | Supervisor           |

| Mr Kenichi Yamazaki   | NTT          | Software Lab   | Research Engineer    |

| Mr Kazuhiro Kazama    | NTT          | Software Lab   | Research Engineer    |

| Mr Katsuto Nakajima   | Mitsubishi   | Info.Sys.Lab   | Senior Researcher    |

| Mr Hiroshi Nakashima  | Mitsubishi   | Info.Sys.Lab   |                      |

| Mr Toshiaki Tarui     | Hitachi      | Central Lab    |                      |

| Mr Takayuki Nakagawa  | Hitachi      | Central Lab    |                      |

| Mr Koichi Kumon       | Fujistu Lab  |                |                      |

| D: Tsutomu Maruyama   | NEC          | C&C Sys. Lab   |                      |

| Mr Takashi Usuki      | Sony         |                |                      |

| Dr Synichi Sakai      | ETL          |                |                      |

| Mr Kenji Nishida      | ETL          |                |                      |

| Mr Hiroichi Hiroshige | ICOT         |                | Executive Director   |

| Dr Kazuhiro Fuchi     | ICOT         | Res.Center     | Director             |

| Dr Kōichi Furukawa    | ICOT         | Res.Center     | Deputy Director      |

| Mr Takashi Kurozumi   | ICOT         | Res.Center     | Deputy Director      |

| Mr Yoshihisa Ogawa    | ICOT         | Res.Plan.Dpt.  | Manager              |

| Dr Shunichi Uchida    | ICOT         | Research Dpt.  | Manager              |

| Dr Ryuzo Hasegawa     | ICOT         | 4&5th Lab      | Deputy Manager       |

| Mr Kenji Ikoma        | ICOT         | Research Dpt.  | Deputy Manager       |

| Mr Tsutomu Yoshioka   | ICOT         | Research Dpt.  | Managing Researcher  |

| Dr Kazunori Ueda      | ICOT         | 2nd Lab        | Senior Researcher    |

| Mr Kuniaki Mukai      | ICOT         | 3rd Lab        | Senior Researcher    |

| Dr Takashi Chikayama  | ICOT         | 2nd Lab        | Chief                |

| Dr Katsumi Nitta      | ICOT         | 7th Lab        | Chief                |

| Dr Kazuo Taki         | ICOT         | 1st (7th) Lab  | Chief (Deputy Chief) |

| Mr Kazumasa Yokota    | ICOT         | 3rd Lab        | Chief                |

| Mr Yuichi Tanaka      | ICOT         | 6th Lab        | Chief                |

| Dr Akira Aiba         | ICOT         | 4th Lab        | Deputy Chief         |

| Mr Nobuyuki Ichiyoshi | ICOT         | 7th Lab        | Deputy Chief         |

| Mr Masayuki Fujita    | ICOT         | 5th Lab        | Deputy Chief         |

| Dr Keiji Hirata       | ICOT         | 1st Lab        | Researcher           |

| Mr Yü Inamura         | ICOT         | lst Lab        | Researcher           |

| Mr David J. Hawley    | ICOT         | 4th Lab        | Researcher           |

| Mr Hiroshi Yashiro    | ICOT         | 2nd Lab        | Researcher           |

# Second Joint ICOT/DTI-SERC Workshop $\mathbf{PROGRAMME}$

(Tokyo Oct.15~17, 1990)

# 10/15 (MONDAY)

At Shiba Park Hotel (Botan-no-ma)

| At Sittod Park I | Iotel (Botan-no-ma)                                  |  |

|------------------|------------------------------------------------------|--|

| 10:00~11:30      | Morning Session (1)                                  |  |

|                  | Chairperson: K. Furukawa                             |  |

| 10:00~10:10      | H. Tanaka: Welcome                                   |  |

| 10:10~10:50      | S. Uchida: Overview of the Final Stage R&D           |  |

|                  | of FGCS Project                                      |  |

| 10:50~11:30      | P. Refenes: Overview of Parallel Computing Research  |  |

|                  | in the UK and Europe                                 |  |

| 11:30~11:50      | { Break (20 min.)}                                   |  |

| 11:50~12:30      | Morning Session (2)                                  |  |

|                  | Chairperson: N. Ichiyoshi                            |  |

| 11:50~12:30      | K. Hirata: PIM Architectures and R&D Status          |  |

| 12:30~14:00      | { Lunch (90 min.)}                                   |  |

|                  | at Ivy room (Shiba Park Hotel Annex 2F)              |  |

| 14:00~15:30      | Afternoon Session (1)                                |  |

|                  | Chairperson: D.H.D. Warren                           |  |

| 14:00~14:40      | Y. Inamura and K. Nakajima: Evaluation of the        |  |

|                  | KL1 Implementation on the Multi-PSI                  |  |

| 14:40~15:30      | P. Townsend: Benchmarking and Evaluation of Software |  |

|                  | Systems – the EDS and Flagship Projects              |  |

| 15:30~16:00      | { Coffee Break (30 min.) }                           |  |

| 16:00~17:30      | Afternoon Session (2)                                |  |

|                  | Chairperson: C. Hughes                               |  |

| 16:00~16:50      | T. Chikayama: Research on Parallel Inference Systems |  |

|                  | in the FGCS Project                                  |  |

| 16:50~17:30      | H. Yashiro: KL1 Programming Environment -PIMOS-      |  |

| 18:30∼           | { Reception }                                        |  |

|                  | at Rose room (Shiba Park Hotel Annex 2F)             |  |

# 10/16 (TUESDAY)

# $At\ ICOT\ Annex$

| 9:30~11:00         | Morning Session (1)                                 |  |

|--------------------|-----------------------------------------------------|--|

|                    | Chairperson: P. Refenes                             |  |

| 9:30~10:20         | D.H.D. Warren: Progress in the Development          |  |

|                    | of the Data Diffusion Machine                       |  |

| 10:20~11:00        | P. Evans: A Programming Environment                 |  |

|                    | for Parallel MIMD Machines                          |  |

| 11:00~11:20        | { Break (20 min.) }                                 |  |

| 11:20~12:00        | Morning Session (2)                                 |  |

|                    | Chairperson: T. Chikayama                           |  |

| 11:20~12:00        | G. Manning: Decomposition of Parallel Applications  |  |

| 1704               | for SIMD Machines                                   |  |

| $12:00{\sim}13:30$ | { Lunch (90 min.) }                                 |  |

| $13:30{\sim}14:50$ | Afternoon Session (1)                               |  |

|                    | Chairperson: A. Goto                                |  |

| 13:30~14:10        | N. Ichiyoshi:                                       |  |

|                    | Parallel Application Program Research at ICOT       |  |

| 14:10~14:50        | R. Hasegawa: MGTP: A Hyper-Matching                 |  |

|                    | Model-Generation Theorem Prover                     |  |

|                    | with Ramified Stacks                                |  |

| $14:50{\sim}15:20$ | { Coffee Break (30 min.) }                          |  |

| $15:20{\sim}16:50$ | Afternoon Session (2)                               |  |

|                    | Chairperson: Y. Inamura                             |  |

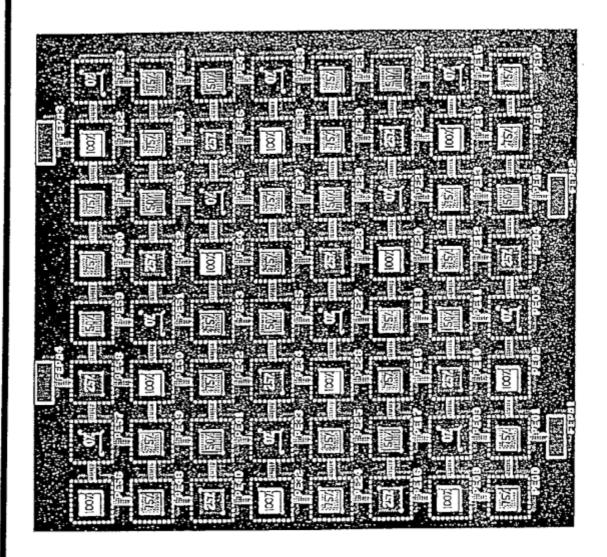

| 15:20~16:10        | K. Taki: Parallel Programming in VLSI CAD Systems   |  |

| 16:10~16:50        | K. Nitta: Parallel Programming                      |  |

|                    | in Genome Analysis System                           |  |

| $16:50{\sim}17:30$ | Afternoon Session (3)                               |  |

|                    | Chairperson: K. Hirata                              |  |

| 16:50~17:30        | D. Hawley and A. Aiba: Constraint Logic Programming |  |

|                    | and Its Parallel Implementation:                    |  |

|                    | Guarded Definite Clauses with Constraints           |  |

# 10/17 (WEDNESDAY)

# $At\ ICOT\ Annex$

| 9:30~10:20  | Morning Session (1)                                         |  |

|-------------|-------------------------------------------------------------|--|

|             | Chairperson: K. Ueda                                        |  |

| 9:30~10:20  | J.Darlington: Mapping Applications onto Various Parallel    |  |

|             | Architectures using Functional Language                     |  |

|             | and Program Transformation                                  |  |

| 10:20~10:30 | { Break (10 min.) }                                         |  |

| 10:30~12:00 | Morning Session (2)                                         |  |

| 10:30~12:00 | Mini Panel: (Title to be announced)                         |  |

|             | Coordinator: K.Furukawa                                     |  |

|             | Panelists: D.Warren, J.Darlington, T.Chikayama, N.Ichiyoshi |  |

| 12:00~13:30 | { Lunch (90 min.) }                                         |  |

| 13:30~17:50 | Demonstrations                                              |  |

| 13:30~13:40 | Overview of the demonstrations                              |  |

|             | 1) Parallel systems                                         |  |

|             | (Written in KL1 and running on the Multi-PSI/PIMOS)         |  |

| 13:40~14:15 | Pentomino-Packing Piece Puzzle Solver                       |  |

|             | Bestpath-Shortest Path Problem Solver                       |  |

| 14:15~14:30 | Go-playing program: GOG                                     |  |

| 14:30~15:00 | { Coffee Break (30 min.) }                                  |  |

| 15:00~15:30 | LSI CAD program (Routing)                                   |  |

|             | LSI CAD program (Logic Simulation)                          |  |

| 15:30~15:55 | Functional Programming Environment                          |  |

| 15:55~16:00 | { Break (5 min.) }                                          |  |

| 16:00~16:25 | Legal Reasoning program                                     |  |

| 16:25~16:50 | Genome Analysis programs                                    |  |

| 16:50~17:00 | { Coffee Break (10 min.) }                                  |  |

|             | 2) Sequential systems                                       |  |

|             | (Written in ESP and running on the PSI/SIMPOS)              |  |

| 17:00~17:25 | Constraint logic programming language: CAL                  |  |

| 17:25~17:50 | Molecular Biological Database in Kappa                      |  |

| 18:30~21:00 | { Farewell party }                                          |  |

|             | at "Chugoku Hanten" (Chinese restaurant)                    |  |

# Overview of the Final Stage R&D of FGCS Project

Shunichi UCHIDA Institute for New Generation Computer Technology (ICOT)

September 30, 1990

### Extended Abstract

FGCS project was substantially started from June 1982. Roughly speaking, it aimed at the R&D of following three major technological goals;

- 1. Knowledge processing

- 2. Parallel processing

- 3. Combination of above two using Logic programming

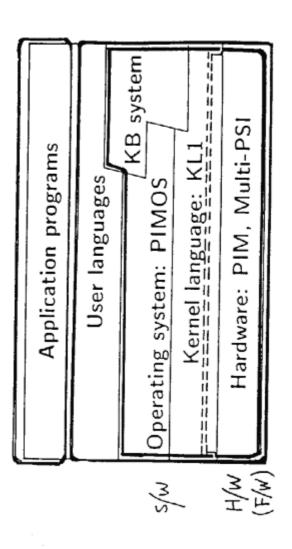

Since then, the project has developed following hardware and software systems for the research on parallel processing;

- Sequential inference systems

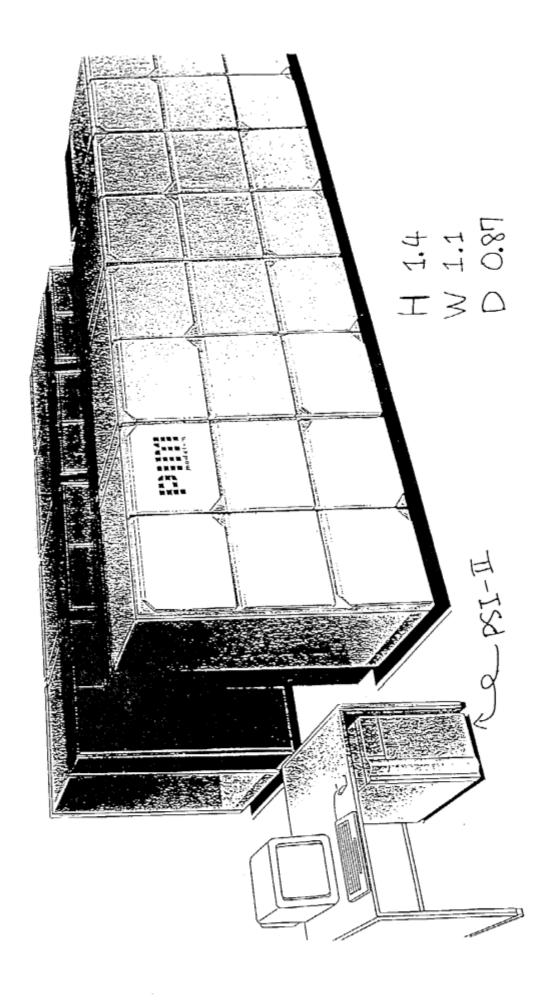

- 1984 PSI-I attaining 37 KLIPS (KL0) and ESP language and SIMPOS

- 1986 PSI-II attaining 330 KLIPS (KL0)

- 2. Parallel inference systems

- 1985 GHC

- 1986 Multi-PSI/V1 attaining 1 KLIPS x 6PE (FGHC), and Parallel interpreter of FGHC

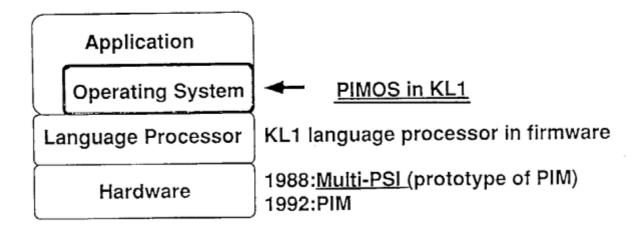

- 1988 Multi-PSI/V2 attaining 150 KLIPS x 64PE (KL1), and PIMOS/V1 and small benchmark programs

- 1990 VLSI chips and CPU boards for final PIM modules, and PIMOS/V2 and many small application programs

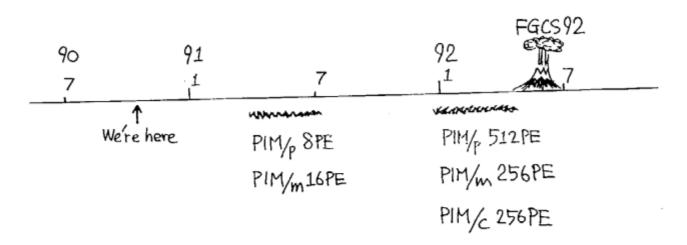

- 1992 Final PIM modules, 256-512PE x 3 modules, attaining 300-400 KLIPS x N (KL1) = Target/module: 200-500 MLIPS and PIMOS + KBMS and medium scale experimental application systems

For the research on knowledge processing, a variety of experimental software systems have been built on the sequential inference system.

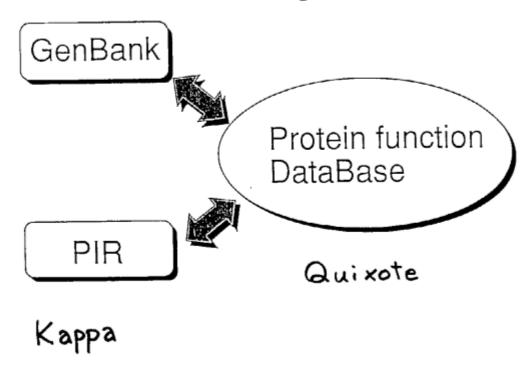

A DBMS based on the nested relational model; Kappa-II, and an experimental system

of deductive and object-oriented DB

### Extended abstract

- An experimental system for natural language understanding; DUALS, and a tool-kit for NL research; LTB

- Constraint logic programming language; CAL

- Expert systems for VLSI design and diagnosis of electronic systems

- Theorem prover and a computer aided proof system; CAP

- A Go-game playing system; GOG

In the final stage, we plan to reconstruct some parts or some functions of these software systems on the parallel inference systems. Furthermore, we try to include such new application areas as genetic information analysis and legal information retrieval.

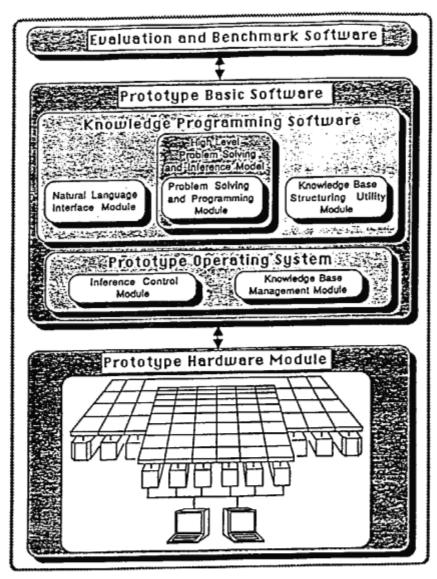

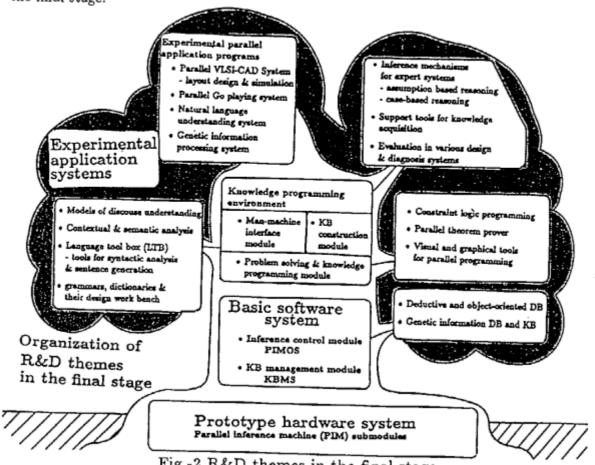

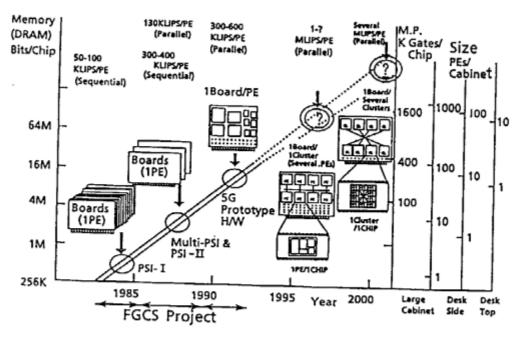

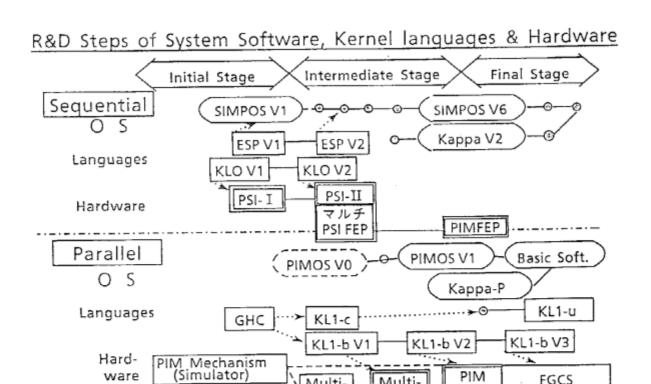

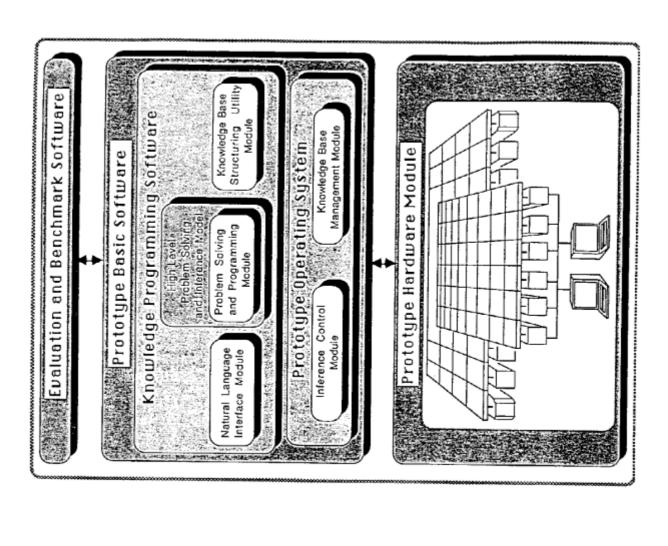

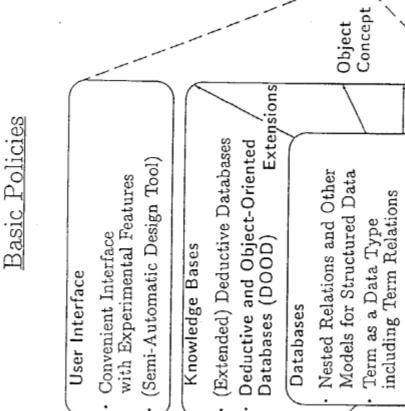

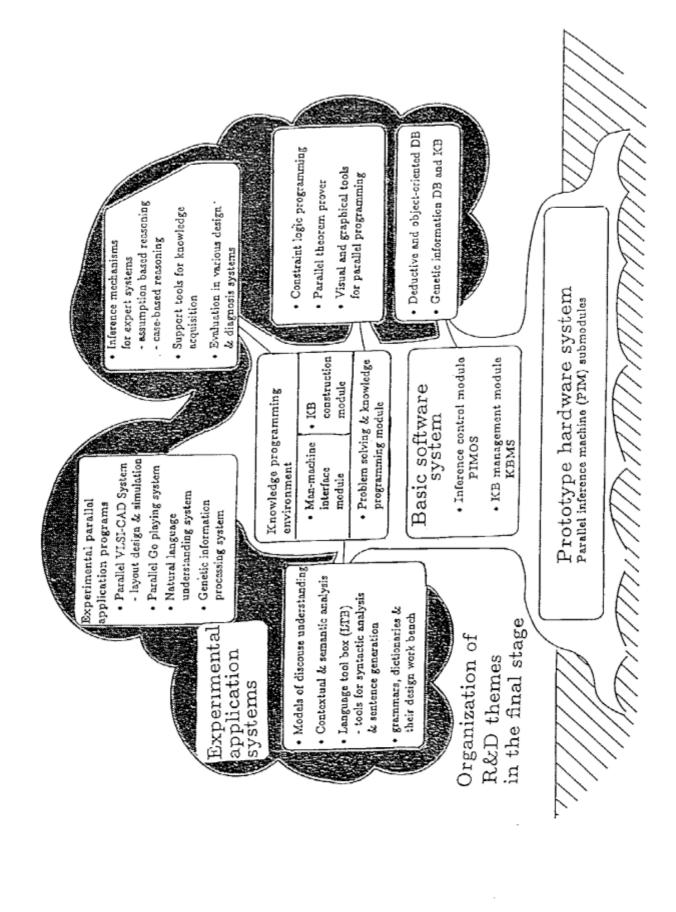

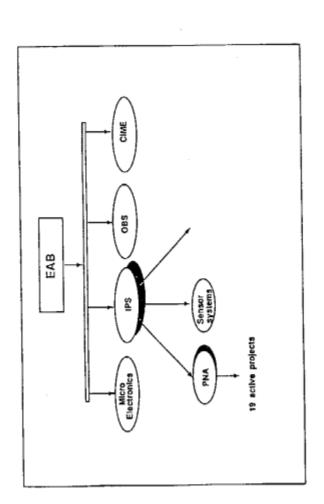

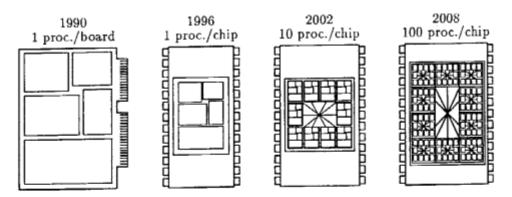

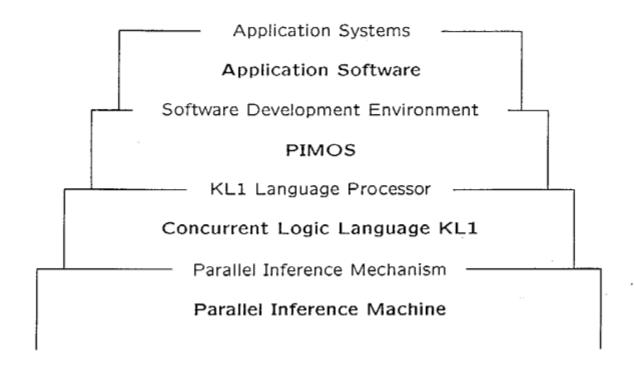

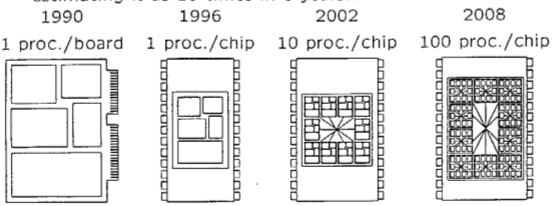

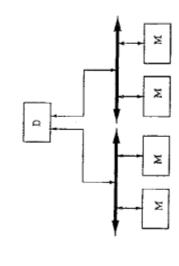

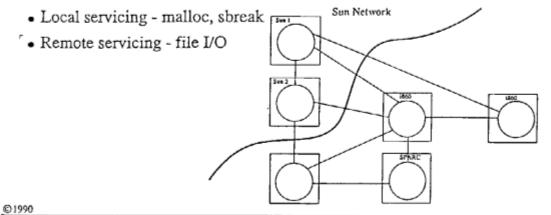

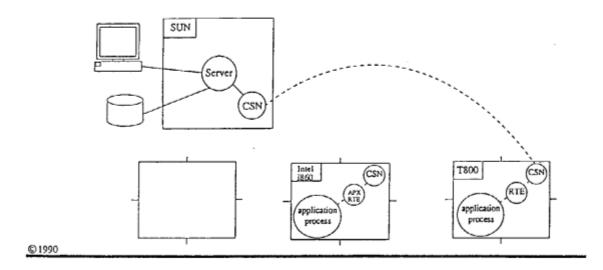

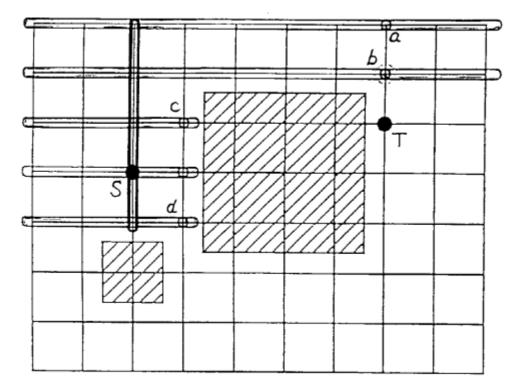

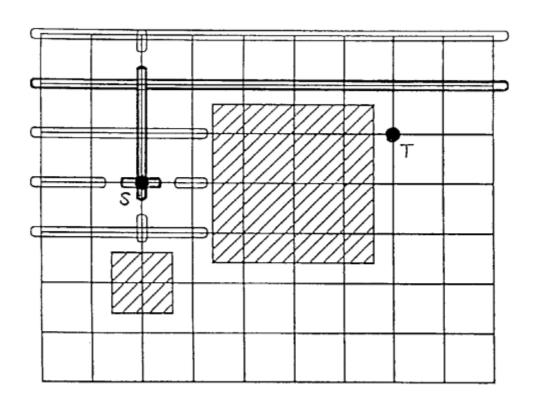

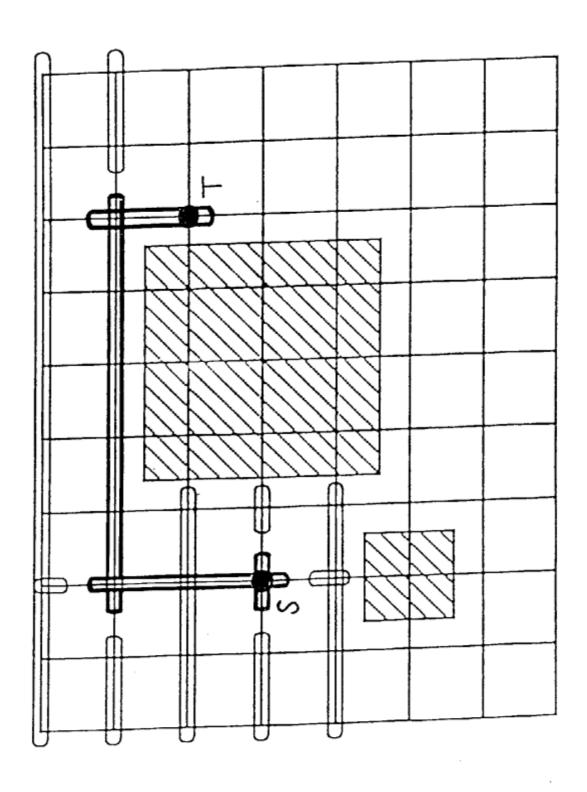

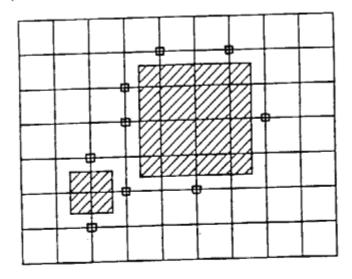

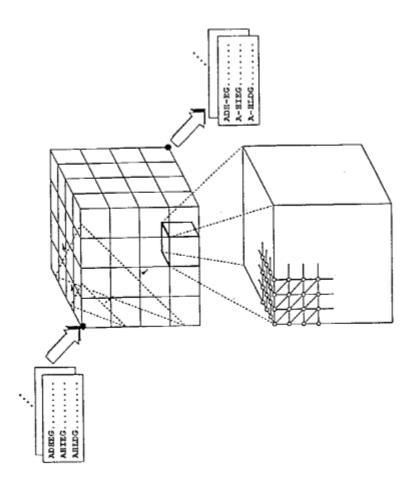

An image of our target system is illustrated in Fig-1. Our research activities in the final stage is illustrated in Fig.-2. The trend of hardware technology which we used for our inference systems is illustrated in Fig.-3.

Fig.-1 The structure of the FGCS prototype system

### Extended abstract

The experimatal parallel application systems are important research topics newly added in the final stage.

Fig.-2 R&D themes in the final stage

Fig.-3 Trend of the hardware technology used for inference machines (by T. Kurozumi)

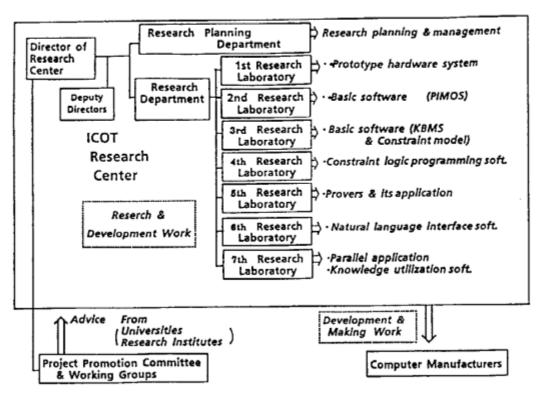

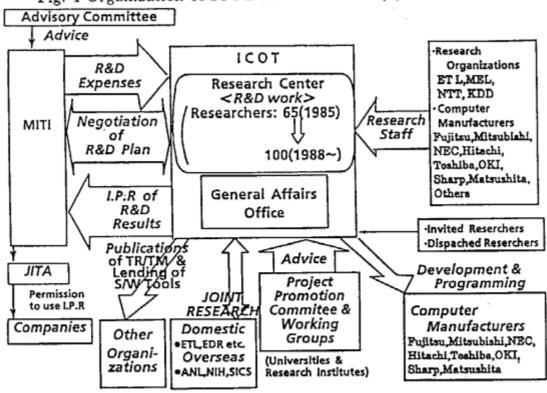

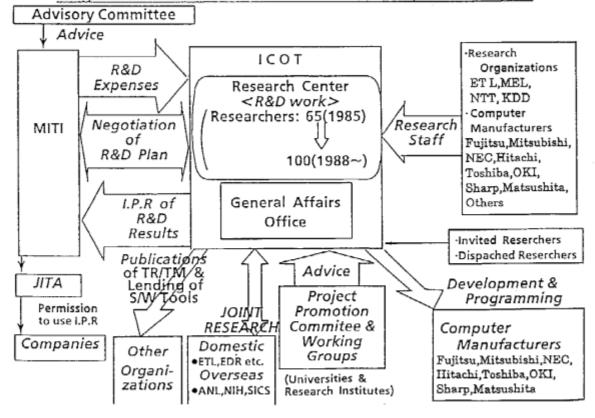

The organization of ICOT has been changed and extended. Recently, we have started international collaborative works with ANL, NIH and SICS using the sequential and parallel inference systems. These are summarized in Fig.-4 and Fig.-5.

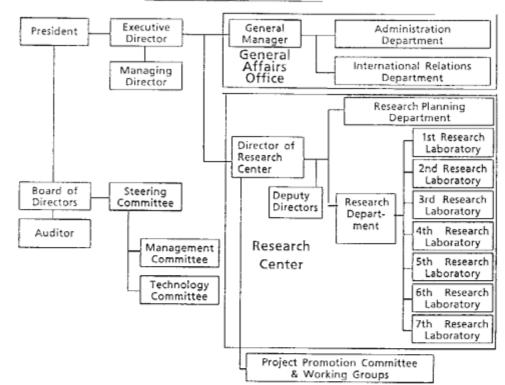

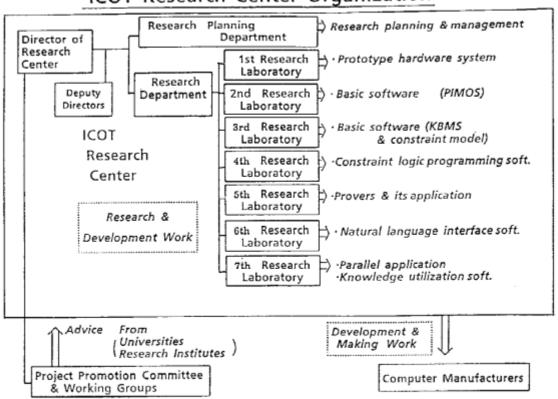

Fig.-4 Organization of ICOT research center (by T. Kurozumi)

Fig.-5 Organization of FGCS project (by T. Kurozumi)

Overview of the Final Stage R&D of FGCS Project

Shunichi Uchida ICOT

- 1984 PSI-I 37 KLIPS (KL0/V1)

-ESP language and SIMPOS/V1

- 1986 PSI-II 330 KLIPS (KL0/V2) -SIMPOS/V2 and Kappa-I

- 1988 -SIMPOS/V5 and Kappa-II

- -Pseudo Multi-PSI and PIMOS-S

- \*\* About 300 PSI-II Machines and Network

- 1991 PSI-III  $\Rightarrow$  1.2 MLIPS (KL0/V2)

- SIMPOS/V7 + UNIX

- -Domestic and international network link

- to access PIM systems at ICOT

Knowledge Programming Software on PSI/SIMPOS

1987 - 1990

- Knowledge Representation Languages:

- CIL, CRL and Quixote

- KBMS based on Deductive and O-O DB

- Constraint Programming Languages: CAL

- Mathematical and Meta-programming Systems: CAP, EUODHILOS, ARGUS, etc

- NL Understanding Systems and Tools: DUALS and LTB

- Many Expert Systems:

- VLSI CAD Systems

- Go playing system

- CASE Systems, etc.

# Parallel Inference Systems

1985 GHC

1986 Multi-PSI/V1 1 KLIPS x 6PE (FGHC)

Parallel interpreter of FGHC

1988 Multi-PSI/V2 150 KLIPS x 64PE (KL1 (2 - 5 MLIPS)

PIMOS/V1 and small benchmark programs

1990 Final PIM Chips and CPU Boards

PIMOS/V2 and many application programs

1992 Final PIM System 300-600 KLIPS/PE (KL1 (PIM model/p ⇒ 200 MLIPS/512PE)

5 modules: model-p, m, c, k, i

Total 1072PE's = 512 + 256 + 256 + 32 + 16

PIMOS/V3 + KBMS(Kappa-P)

Parallel Application Systems

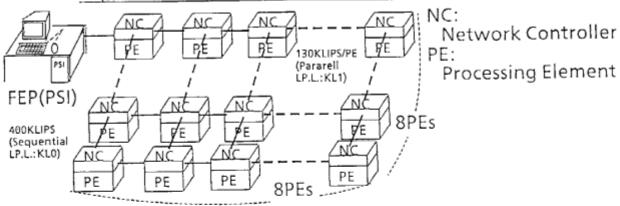

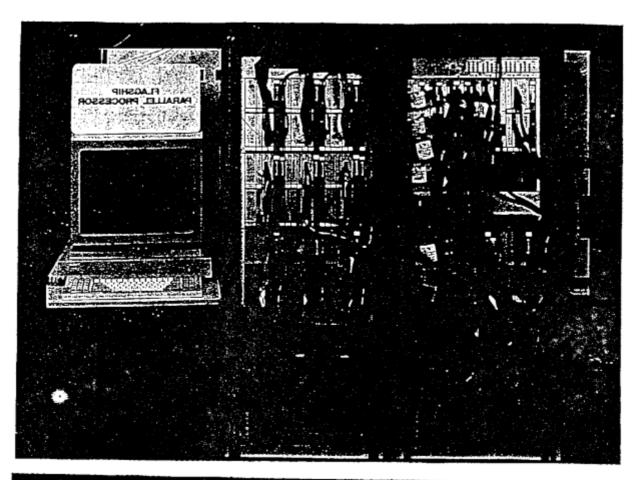

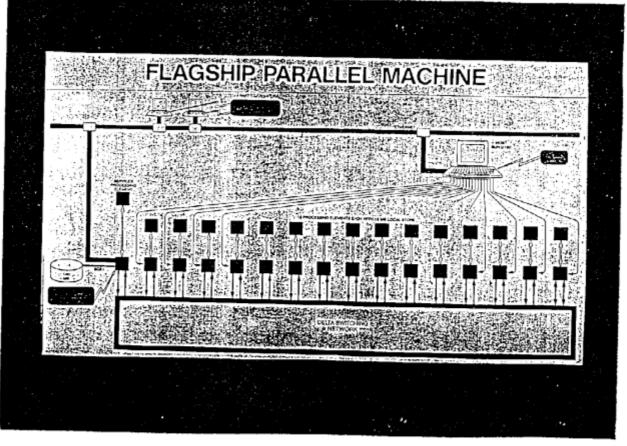

# Experimental Parallel Inference Machine: Multi-PSI/v2

o64 PEs max (PSI-II CPU each) 2 ~ 5MLIPS/system (ave)

Machine language: KL1-b

16 Mw / PE

ware

KBM Mechanism

(Simulator)

(80MB)

Network :

2-dimentional mesh, -message exchange

-routing functions

PIM

KBM

Multi-

PSI V2

**FGCS**

PrototypeH/W

-5MB/s x 2directions/ch

Multi-

PSI V1

# Main research targets in the Final Stage

"To establish a parallel logic programming environment to be able to open for large scale application problems"

- 1. Large-scale high-speed PIM modules

- 2. Reliable multi-user operating system

- 3. Parallel DBMS

- 4. Collection of parallel programming tools and skills through the development of application programs

# 1. PIM hardware modules and KL1 language processors

- Completion of PIM H/W development and evaluation of H/W:

Chips, CPU Boards, Clusters, Cabinets, and Total systems

- Completion of distributed implementation of KL1 language processors in the cluster and total system:

Memory management, Message passing control, and etc.

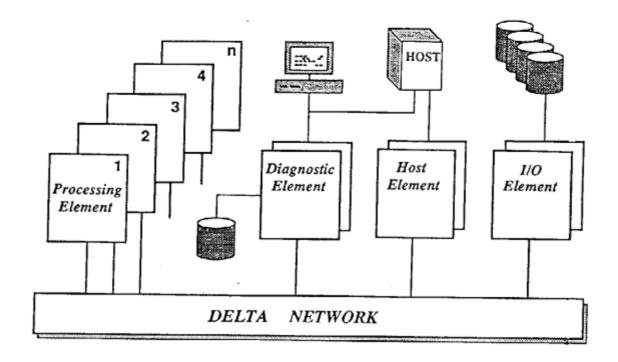

Prototype System Configuration—Parallel Software Developement Environment— -pa-pp ee Hef 60 de -Doble Hypercube-101111 PE, Shared Memory PE Network PE Cluster Bus

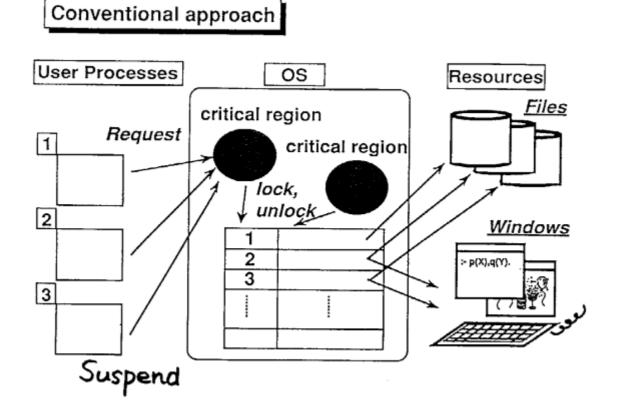

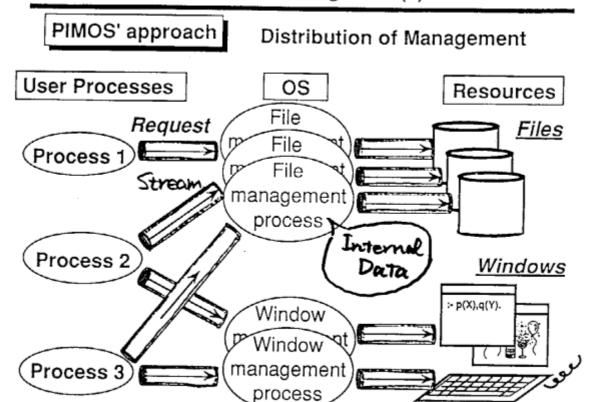

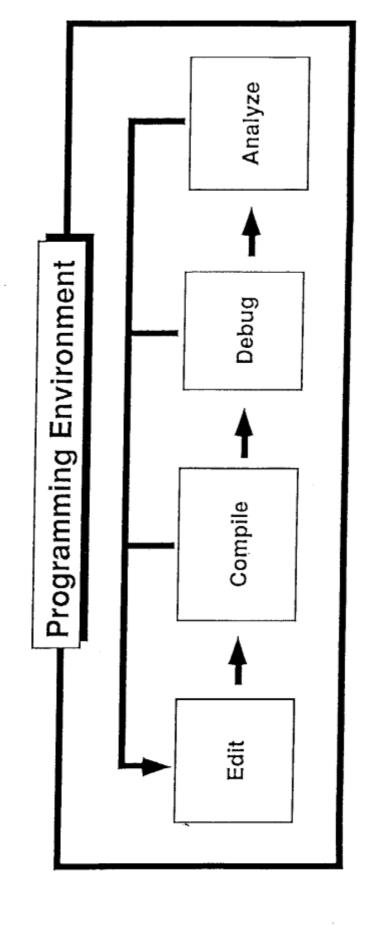

# 2. Operating system, PIMOS

and KL1 programming environment

Improvement and extension of the core of PIMOS: Resource management, Remote Access control, and User management

KL1 programming environment:

Debugging tools including performance debugging, Optimization techniques in Compilers, and etc.

Parallel programming skills:

Algorithms, Paradigms, and Strategy for job division and priority control

# 3. Parallel DBMS and its extension to KBMS

- Development of parallel DBMS, Kappa-P based on Nested Relational Model

- Implementation of relational algebraic operations on parallel and distributed environments, Multi-PSI and PIM

- Design and implementation of KBMS based on Deductive DB and Object-Oriented DB

- Design and implementation of a knowledge representation language, Quixote for the KBMS

# Current Status of the Kappa System

# • Kappa-I was implemented in August, 1987

- 60,000 Lines in ESP

- Several β-Test Users

# Kappa-II was implemented in March, 1989

- 125,000 Lines in ESP

- More Efficient Performance Than Kappa-I

- Main Memory Databases

- User Definable Interface

- Practical Constructors (List, Bag)

- Widely Released

# Kappa-P will be implemented in March, 1991

- Written in KL1

- Parallel Version of Kappa-II

in a Distributed Environment

Efficient Performance

· (More Efficient Performance Than Kappa-II?)

# 4. Application systems for parallel inference system including DBMS/KBMS

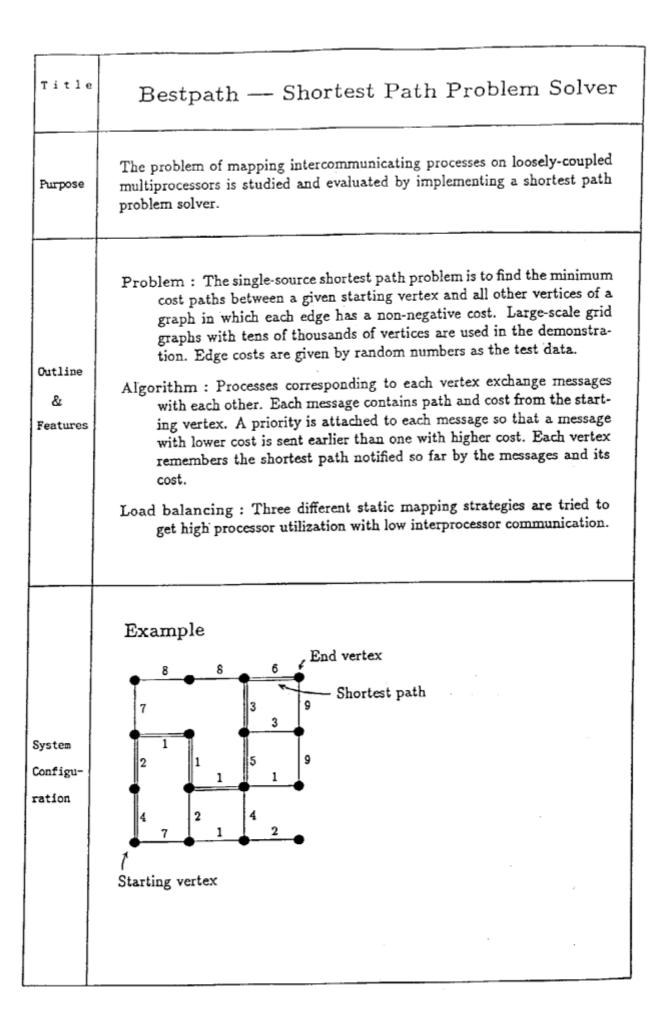

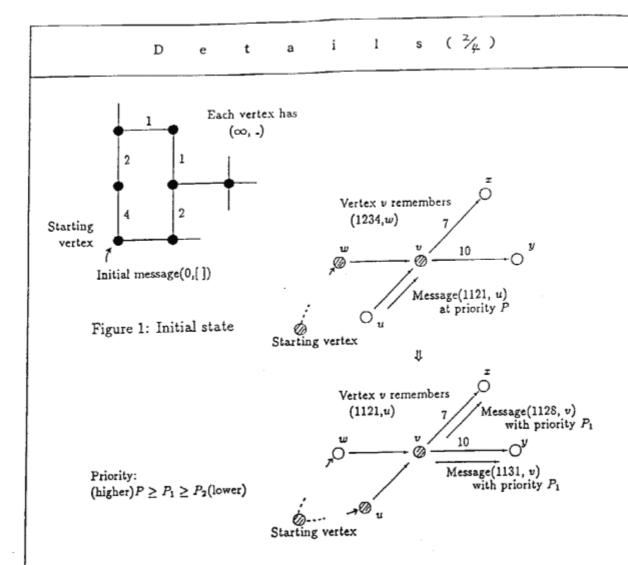

(a) Small benchmarking programs:

Best-path, Pentomino and Tume-Go programs

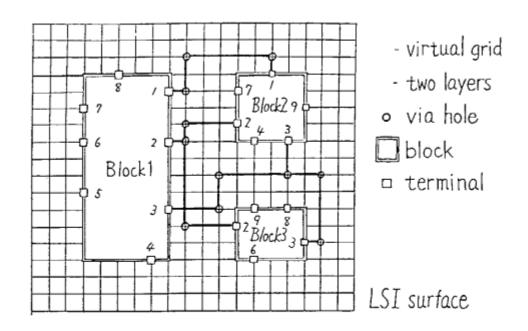

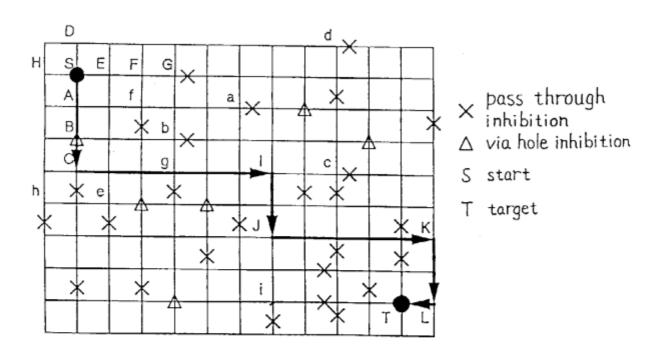

(b) Routing and logic simulation programs for VLSI CAD systems

(c) Parsers for lexical and syntactic analysis in NL understanding systems

(d) Parallel Theorem Provers

(e) Parallel implementations of Constraint Logic Programming Language, GDCC

- (f) Parallel Go playing system, GOG

- (g) Legal reasoning programs

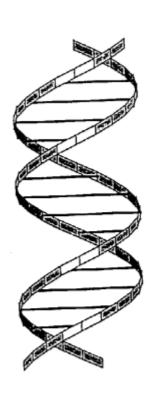

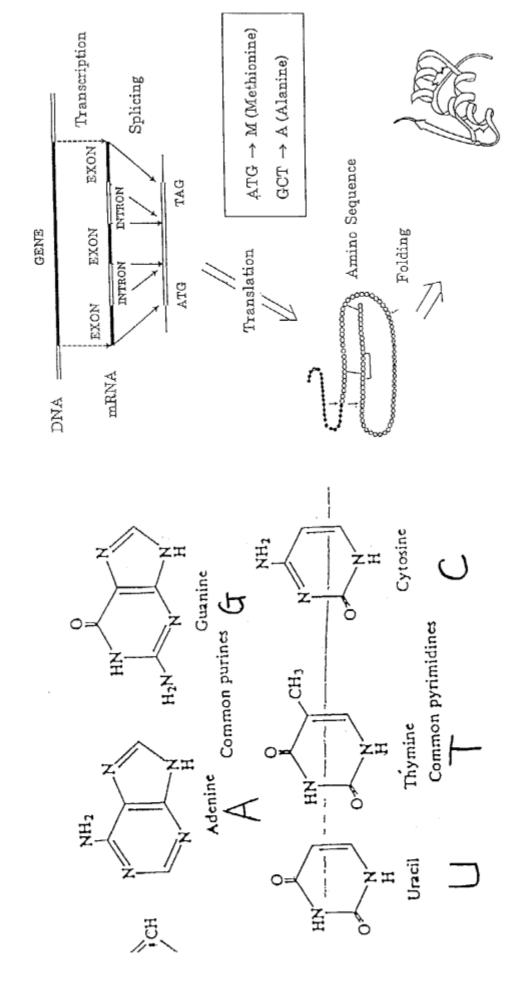

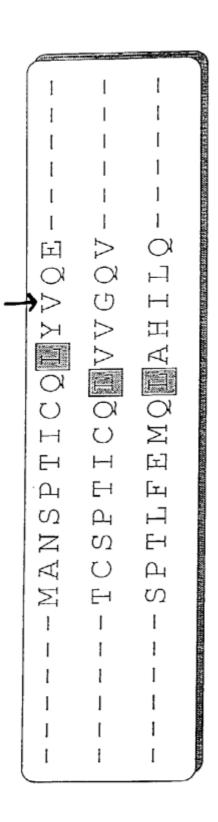

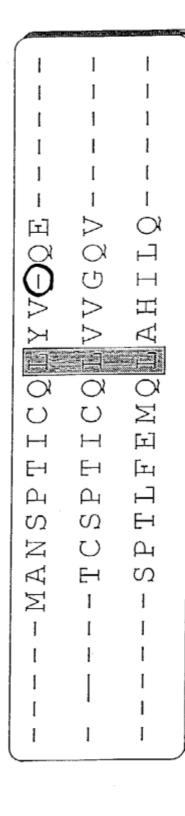

- (h) Programs for multiple sequence alignment of DNA or protein sequences for genetic information analysis

- (i) Evaluation of Kappa-II using GenBank data and description of metabolic reactions using the knowledge representation language, Quixote

### Desk 10 Top 110001 100 1 PEs/ Cabinet Desk Side Size 100 TRENDS of LSI TECHNOLOGIES & 5G MACHINES 10 Large Cabinet K Gates/ Chip 1600 100 400 <u>M</u>.P. 1Board/ Several Clusters מ מי ש ರ 1Cluster /1CHIP 2000 Several MLIPS/PE (Paraliel)g ಕ ಕ Year 1Cluster (Several.PEs) 1PE/1CHIP MLIPS/PE (Parallel) × 1-7 1Board/ 1995 Prototype l H/W ..... Board/PE 5G (Parallel) KLIPS/PE Multi-PSI & PSI - II 300-600 1990 FGCS Project (Sequential) 130KLIPS/PE (Parallel) KLIPS/PE Boards (1PE) PSI-I 300-400 1985 (Sequential) Boards (1PE) KLIPS/PE 50-100 **256K** 16M 64M ₹ Bits/Chip 4⊠ Memory (DRAM)

### Stages of & Budget for FGCS Project R&D (10- year plan) Preliminary Initial Stage Final Stage Intermediate Stage Study 3 years: '82~'84 4 years: '85~'88 3 years: '89~'91 Stage (M00E,8x: JATOT) (TOTAL: x21,600M) 1979~1981 o R&D of Basic 5th G. R&D of Experimental e R&D of Total Computer Technology Small-Scale Subsystem (Prototype) System Budget: 1982 1986 1983 1984 1985 1987 1988 1990 1989 (for each ¥400M ¥2.7B ¥5.1B ¥4.7B ¥5.55B ¥5.6B ¥5.7B ¥6.5B ¥7.0B fisical \$1.86M+1 \$12.6M \$23.7M \$21.9M \$34.5M\*2 \$35.0M \$35.6M \$40.6M \$43.7M

· R&D are carried out under the auspices of MITI.

(All budget are covered by MITY.)

£22.8M I

£26.0M

£27.4M

£22.0M+2 £22.4M

\*1 \$1 = \forall 215, £1 = \forall 307 (1982~1985)

£15.3M

£16.6M

year)

£1.30M+1 £8.80M

\*2 \$1 = \(\forall 160, \(\xi\)1 = \(\forall 250 \)(1986\(\tau\)1989)

# ICOT Organization

ICOT Research Center Organization

Organization of Fifth Generation Computer Project

# International Co-operation & Diffusion Activities of R&DResults

· Preparation and Distribution of Technical Papers

(e.g., ICOT Journal, Technical Reports and Memoranda(1,400 TR/TMs))

· Conferences and Symposia

· Sponsorship of the International Conference on FGCS

(1981, 1984, November 1988,1st-5th June 1992(planning))

· Joint Symposia and Workshops(co-sponsorship)

....U.S.-J , France-J , Sweden-Itary-J , U.K.-J

·Invitation of Experts (Researchers)

to ICOT for short periods for research exchange (56 researchers(1982-1989))

- -backed)& U.K(DTI-backed) to ICOT for half to 1 year (based on agreement) Acceptance of Researchers from U.S.(NSF-backed), France(INRIA

- Dispatch of researchers (universities, ICOT)

to international Conferences and Meetings to present technical papers

- · Acceptance of visitors to ICOT (Researchers, Journalists, etc.)

- · Joint Research with other Organizations ....ANL, NIH, SICS,

# OVERVIEW OF PARALLEL COMPUTING RESEARCH IN THE UK AND EUROPE

### PAUL REFENES

INFORMATION TECHNOLOGY DIVISION

DEPARTMENT OF TRADE AND INDUSTRY

### ABSTRACT

Parallel and novel architecture research is a research area which is becoming increasingly important for the IT Industry as a whole. The majority of the novel programming styles and computational models which are expected to enhance programmer productivity (e.g. Functional, Logic, Object-Oriented, etc) have a strong requirement for powerful compute engines which is beyond the capabilities of traditional sequential processors. In addition an increasing number of new applications are emerging which are only possible to tackle due to the availability of powerful parallel computers.

The research area of parallel and novel architecture encompasses four key technologies:

- hardware architecture: this technology includes both the design of microprocessors/microcomputers and the architecture of networks of such processors.

- basic system software: including operating system kernels, memory management, message through-routing, etc.

- parallel application development tools: such as decomposition tools, mapping tools, load balancing, etc.

- neural computing: soft information processing systems and massively parallel and distributed architectures.

This paper reviews the state of the art in UK and European research in these four areas.

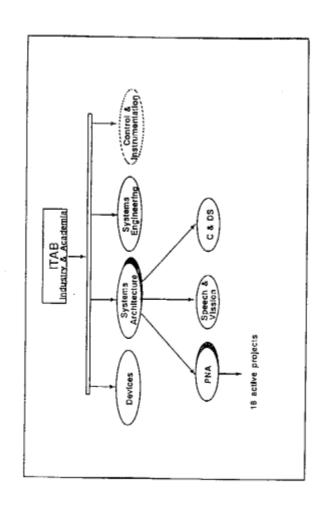

# OVERVIEW OF PARALLEL PROCESSING IN EUROPE & THE UK

P. N. REFENES

INFORMATION TECHNOLOGY DIVISION DEPARTMENT OF TRADE & INDUSTRY

CONTENTS

IT research in the UK

\* IT research in Europe

Parallel Architecture research in Europe & the UK

Symbolic processing

Numeric processing

Basic system software

Parallel application development tools

Neural computing

Parallel Application Centres Programme

2nd Joint ICOT/DTI-°FRC Workshop

Tokyo Oct. 1990

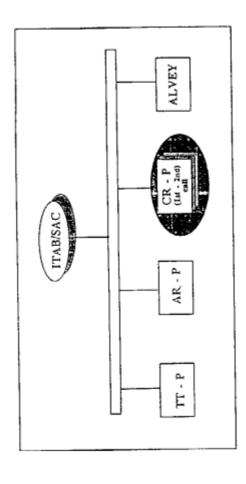

IT research in the UK - ITAB

- Two active calls + old ALVEY projects

- Special Initiatives

- . Parallel applications Programme . Neural Computing

# IT research in Europe - ESPRIT

# - Two active calls

# Much Larger Projects

# ITAB/SAC ACTIVE PROJECTS

TT - P : Technology Transfer Programme (within SAC)

AR - P : Academic Research CR - P : Collaborative Research ALVEY: Projects which are still active

SAC funding - this report deals only with the collaborative/uncolled projects from the 1st and 2nd call.

# 22 3223 23 . 2 2 Numeric processing Badic System Software Application Development Neural Compacing SPEECH& YESON Vision Systems Spench Systems Vision Systems Spench Systems 57.8 57.8 13.9 18.2 22 34.4 19.6 52.63 86223 2222 ä 2323 2 ADVANCED ARCUITECTURE TOTAL SENSOR-BASED SYSTEMS Numeric Processing Batic System Software Application Development Vision Systems (IPS) Speech Systems (IPS) Vision Systems (OBS) Speech Systems (OBS) Distributed Systems Methods & Tools Application Denocate Symbodic Processing Tools Neural Computing

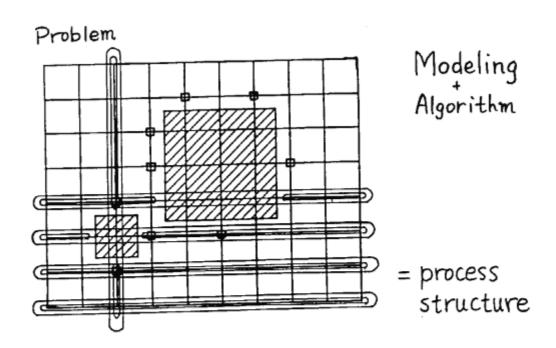

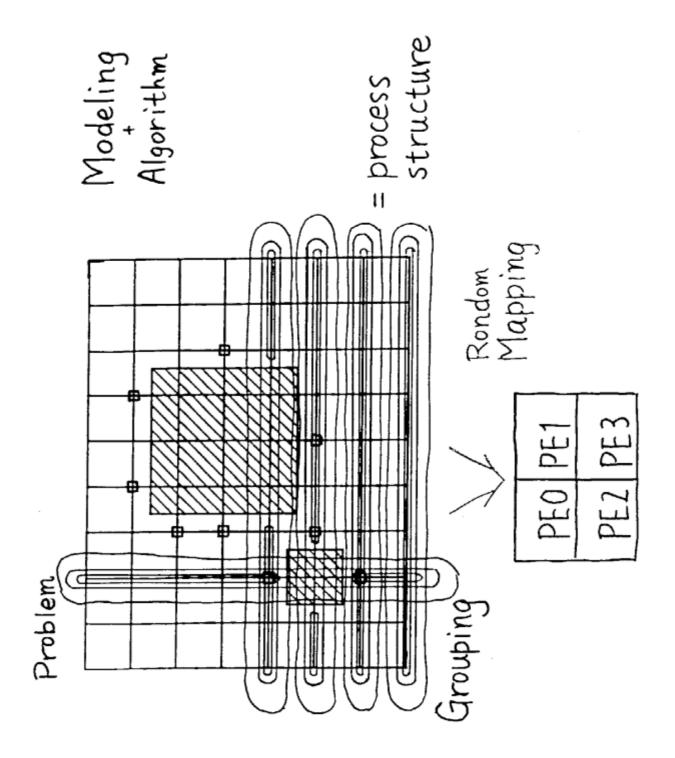

# PARALLEL DECOMPOSITION

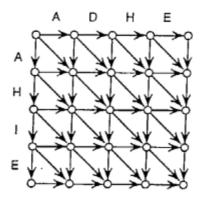

# GEOMETRIC DE-COMPOSIQUON («FMIMD, SIMD)

- Parallelismus obtained by distributing the DATA such that the original geometric structure is preserved

- SXNCHRONISES between computational steps with others Each PE processes MODERATE amounts of data and

OFFEBS good speed-up IF, data dependencies are characterised

LIMITING factor Is, the communication overheads by locality of reference

# EXAMPLE

(Chaotic retaxation)

A[i+1, j] A[I, ]+1] A!', I-1]. AD, [] = f[ A[1-1, ]],

¥

## Parallelism is obtained through a pool of processors executing Little synchronisation is required between processors except OFFERS speed-ups proportional to the # of processors used LIMITING factor is the contention for access to the pool PARALLEL DECOMPOSITION 씸 % troff file & a.cut program & grep x file > Junk & grep Pool of processes Pool of processors FARMING DE-COMPOSITION (cf. MIMD) for the Initlal delivery of data a.out ם from a pool of processes. (Unix processes) troff ם EXAMPLE

pollsh

ďγ

wlpe

wash

car car car car

EXAMPLE

polish(car)

next(car)

wash(car) wipe(car) dry(car)

do (9 to 5) {

Parallelism is obtained by de-composing the ALGORITHM

Into smaller steps.

ALGORITHMIC DE-COMPOSITION (cf MISD)

PARALLEL DECOMPOSITION

STEPS are simple and performed repetitively in a loop Offers speed-ups proportional to the # of processors used

LIMITING factor is the slowest element in the pipeline

## NUMERIC PROCESSING SYSTEMS

## **CHARACTERISTICS**

- \* Highly regular data structures -> geometric parallelism

- \* Highly regular operations -> algorithmic parallelism

- \* Static de-composition

- ->

static processes

static control structures

static languages (Fortran, Occam, Parle, etc)

|                             | E                         | 0.5                                                                              |                                                                              |                                     |   |      | _ |      | 0.5   |

|-----------------------------|---------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------|---|------|---|------|-------|

|                             | ü                         |                                                                                  |                                                                              |                                     |   | <br> |   |      |       |

|                             | ž                         | AMT<br>MEIKO                                                                     |                                                                              |                                     |   | <br> | 1 | <br> | _     |

| PARALLEL NOVEL ARCHITECTURE | (SIMD) PROCESSING         | High speed SIMD/MIMD<br>interconnect                                             |                                                                              |                                     | - |      |   |      | TOTAL |

| ITAB                        | NUMERIC                   | SIMD/<br>MIMD<br>(1428)                                                          |                                                                              |                                     |   |      |   |      |       |

|                             | \$UK                      | 69.3                                                                             |                                                                              | 53.4                                | _ |      |   | <br> | 57.8  |

|                             | UK                        | 6.28                                                                             | 0.0                                                                          | 5.72                                |   |      |   |      | 12.0  |

|                             | MECU                      | 9.06                                                                             | 1.0                                                                          | 10.71                               |   |      |   |      | 20.77 |

| ADVANCED ARCHITECTURE       | PROCESSING: Architectures | Distributed memory parallel<br>Super Computer for numerical<br>applications BULL | Optical processing architecture<br>in industrial applications<br>THOMSON-CSF | General purpose MIMD machines INMOS |   |      |   |      | TOTAL |

| ESPRIT                      | NUMERIC                   | GENESIS<br>(2447)                                                                | NAOPIA<br>(2288)                                                             | GPMIMD<br>(5404)                    |   |      |   |      |       |

TABLE III: Numeric Processing Architectures

## SYMBOLIC PROCESSING SYSTEMS

## CHARACTERISTICS

## **LANGUAGES**

- \* are VHL mostly with IMPLICIT Parallelism

- \* notable tends towards explicit Parallelism to restrict ||ism to manageble levels.

## <u>ARCHITECTURES</u>

- \* higly (micro) programmed control flow devices

- \* need to support dynamic control structures (stacks, etc)

## PARALLELISM

- \* mainly farming de-composition (reduction systems)

- \* also some geometric parallelism in logic (unification)

| ESPRIT            | SYMBOLIC PROCESSING ARCH                                                         | HITECTUR | RES  |              | ITAB             |                                                                                        |                                  |     |

|-------------------|----------------------------------------------------------------------------------|----------|------|--------------|------------------|----------------------------------------------------------------------------------------|----------------------------------|-----|

|                   |                                                                                  | MECU     | UK   | <b>\$</b> UK |                  |                                                                                        | UK                               | £M  |

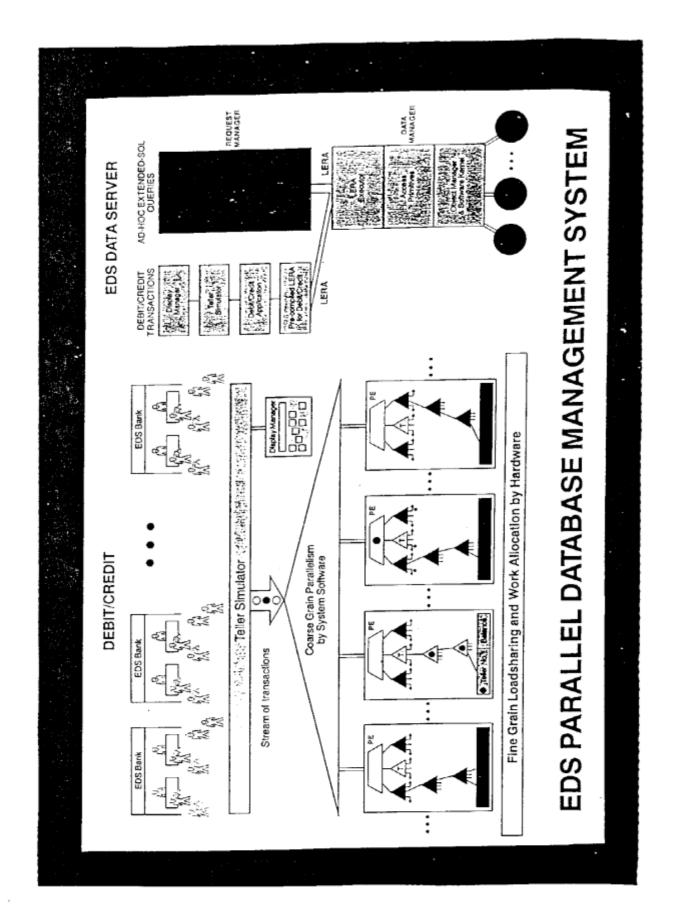

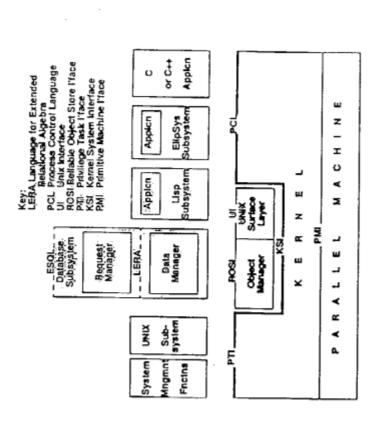

| EDS<br>(2025)     | Successor to Flagship, and<br>PAVLADA but turning into a<br>database project ICL | 28.5     | 3.36 | 11.          | PPKIKB<br>(1154) | Parallel processing within IKBS                                                        | Deduct<br>ive<br>System<br>MEIKO |     |

| TROPICS<br>(2427) | Parallel object-oriented<br>multiprocessor System 5<br>PHILIPS                   | 10.68    | 0.0  | 0.0          | EXHFL<br>(1674U) | Exploitation of parallel<br>hardware using functional<br>languages program transformat | ICSTM                            |     |

| PEPMA<br>(2471)   | Parallel Prolog on multi-<br>processor systems BIM (B)                           | 2.19     | 1.14 | 52.          | FAST<br>(1702U)  | Functional Programming for<br>Transputer Arrays                                        | ICSTM                            | 0.5 |

|                   |                                                                                  |          |      |              |                  |                                                                                        |                                  |     |

|                   |                                                                                  | 7        |      |              |                  |                                                                                        |                                  |     |

|                   |                                                                                  | $\dashv$ |      |              |                  |                                                                                        |                                  |     |

|                   |                                                                                  | -        |      |              |                  |                                                                                        | -                                |     |

|                   |                                                                                  | -        |      |              |                  |                                                                                        | -                                |     |

|                   |                                                                                  | -        |      |              |                  |                                                                                        | -                                |     |

|                   | TOTAL                                                                            | 41.37    | 4.5  | 10.9         |                  | TOTAL                                                                                  | -                                | 1.0 |

TABLE IV: Symbolic Processing Architecture

## 03

| ESPRIT ADVANCED ARCHITECTURE |                                                                                  |       | ITAB PARALLEL NOVEL ARCHITECTURE |             |                   |                                                                         |              |     |

|------------------------------|----------------------------------------------------------------------------------|-------|----------------------------------|-------------|-------------------|-------------------------------------------------------------------------|--------------|-----|

| Basic S                      | ystem Tools                                                                      | MECU  | UK                               | <b>¥</b> UK | Basic S           | ystem Tools                                                             | UK           | £H  |

| SAPHIRE<br>(1277)            | PCTE portability<br>CAP                                                          | 29.9  | 2.6                              | 8.7         | FTMS<br>(1101)    | Fault /tolerant multi-<br>processor systems<br>Meiko Plessey Perihelion | RSRE         | 1.3 |

| PAVE<br>(1282)               | PCTE and VMS environment<br>GEC                                                  | 1.0   | 0.55                             | 55          | SAFEMOS<br>(1036) | Totally verified systems                                                | INMOS<br>SRI | 1.5 |

| MERMAID<br>(2046)            | Metrification and resource<br>modelling aid<br>VOLMAC (NL)                       | 3.44  | 1.23                             |             | 6<br>SIMD/C       | SIMD extensions to the programming language C                           |              | 0.2 |

| SUPERNODE<br>II<br>(2528)    | Operating systems and programming environments for parallel computers. Thorn EMI | 11.9  | 1.77                             | 14.4        | 37                |                                                                         |              |     |

| COMPARE<br>(5399)            | Compiler Generation for<br>Parallel Machines                                     | 6.41  | 1.17                             | 18.3        | ]<br>             |                                                                         |              |     |

|                              |                                                                                  |       |                                  |             |                   |                                                                         | _            |     |

| *****                        |                                                                                  |       |                                  |             | -                 |                                                                         | .            |     |

|                              |                                                                                  |       |                                  |             |                   |                                                                         | -            |     |

|                              | TOTAL                                                                            | 52.65 | 7.32                             | 13.9        | ,                 | TOTAL                                                                   | _            | 3.0 |

TABLE V: Besic Systems Tools

| ESPRIT          | ADVANCED ARCHITECTURE                                                    |       |      |      | ITAB                      | PARALLEL & NOVEL ARCHITECTURE                                        |                             |     |

|-----------------|--------------------------------------------------------------------------|-------|------|------|---------------------------|----------------------------------------------------------------------|-----------------------------|-----|

| PARALLE         | L APPLICATION DEVELOPMENT TOOLS                                          | MECU  | UK   | ŧ∪ĸ  | APPLICAT                  | ION DEVELOPMENT TOOLS                                                | UK                          | £M  |

| IMSE<br>(2143)  | Integrated Modelling Support<br>Environment STC                          | 3.0   | 1.07 | 35.  | 67<br>  COOTS<br>  (1059) | Object Orientated Languages<br>on Parallel Transputer -<br>Arrays    | RSRE<br>INMOS<br>THORN      | 1.5 |

| REX<br>(2080)   | Reconfigurable and Extensible parallel and distributed systems. STOLIMAN | 9.99  | 1.7  | 17.0 | 02<br>DAPW<br>(1438)      | Programming Work Bench for a<br>Massively Parallel Computer<br>(DAP) | EMI<br>AMT<br>OMW<br>Inter- | 0.: |

| FAAST<br>(5212) | Fault-Tolerant Architecture<br>Nixdorff                                  | 6.58  | 0.22 | 3.3  | FSPP<br>(1452)            | Fortran for Scalably parallel processors                             | MEIKO                       | 0.5 |

|                 |                                                                          |       |      | *    | FLARE<br>(2117)           | Functional Languages Applied<br>to Realistic Examples                | BT<br>Logica                | 0.6 |

|                 |                                                                          |       |      |      | GRAS-<br>PARC<br>(2172)   | Graphical Environmental for<br>Supporting Parallel Computing         | NAG<br>Quin-<br>tel         | 0.5 |

|                 |                                                                          | ,     |      |      |                           |                                                                      |                             |     |

|                 |                                                                          |       |      |      |                           |                                                                      |                             |     |

|                 |                                                                          |       |      |      |                           |                                                                      |                             |     |

|                 | TOTAL                                                                    | 19.57 | 2.99 | 15.3 | 3                         | TOTAL                                                                |                             | 4.0 |

TABLE VI: Parallel Application Development Tools

5

| ESPRIT                       | ADVANCED ARCHITECTURES                                                               |       |      |                     | ITAB PA              | RALLEL NOVEL ARCHITECTURE                                                |                         |     |

|------------------------------|--------------------------------------------------------------------------------------|-------|------|---------------------|----------------------|--------------------------------------------------------------------------|-------------------------|-----|

| NEURAL COMPUTING MECU UK NUK |                                                                                      |       |      | NEURAL COMPUTING UK |                      |                                                                          |                         |     |

| PYGMALION<br>(2059)          | Neurocomputing:                                                                      | 2.5   | 0.45 | 18.                 | GANNET<br>(1886)     | Neural Network<br>generation adoptation<br>using evolutionary techniques | LOGICA<br>MEIKO         | 0.2 |

| ANNIE<br>(2092)              | Industrial application of<br>Artificial Neural Networks<br>UK AEA                    | 2.5   | 1.16 | 46.                 | LINNET ( )           | Neural Network Awareness Club                                            | LOGICA<br>TSB           |     |

| MLT<br>(2154)                | Machine Learning Toolkit.<br>and Industrial Applications<br>NIXDORF                  | 6.99  | 1.68 | 24.0                | 3<br>SRT<br>(1057)   | Speech recognition techniques<br>using Market Chains Neural<br>Networks  | SINTEX<br>CAL<br>PARSYS |     |

| GALATHEA<br>(5293)           | Contination of PYGMALION<br>OM. Architectures, tools and<br>applications THOMSON CSF | 8.5   | 0.84 | 9.5                 | LNNCI<br>(1005U)     | Logica Neural Nets<br>Characteristics and<br>implementation              | BRUNEL                  | 0.2 |

| NNF<br>(5433)                | Neural network systems for forcasting and diagnosis (B)                              | 1.9   | 0.0  | 0.0                 | CONNET<br>(2163)     | Neural Networks for control of real-time systems                         | DOWTY<br>LOGICA         | 0.5 |

|                              |                                                                                      |       |      |                     | EX-STATIO<br>(2167U) | Simulation of dynamic<br>architecture for neural<br>networks             | CAM<br>BRIDGE           | 0.2 |

|                              |                                                                                      |       |      |                     |                      |                                                                          |                         |     |

|                              |                                                                                      |       |      |                     |                      |                                                                          |                         |     |

|                              | TOTAL                                                                                | 22.39 | 4.13 | 18.4                |                      | TOTAL                                                                    |                         | 2.2 |

TABLE VII: NEUROCOMPUTING

## PARALLEL APPLICATION CENTRES PROGRAMME

## AIM:

To establish 4-5 centres to support the tools and methods for the development of parallel applications.

## ACTORS:

Universities :- hosts for the centres

Parallel systems (software & hardware) vendors:- joint projects for further systems development

End Users :- collaborative projects for technology transfer and demonstrators

## TOTAL COST:

up to 40m PS.

## PIM Architectures and R & D Status

Keiji Hirata

Institute for New Generation Computer Technology

hirata@icot.or.jp

## 1 Introduction

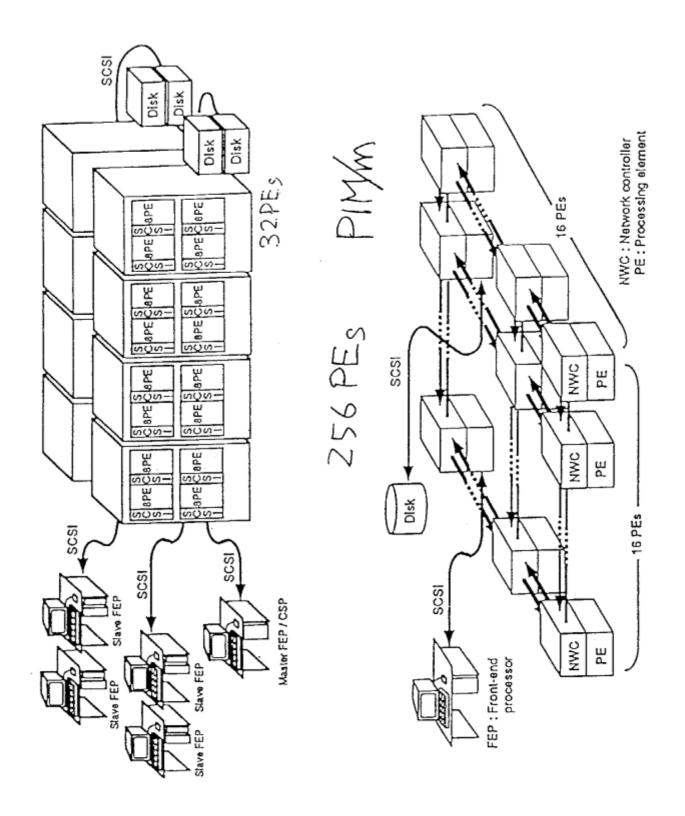

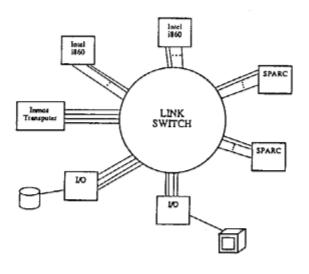

We have been developing parallel inference machines (PIMs) and its firmware in the Japanese FGCS project [Goto 89a], [Goto 89a]. Our research goal is to prove that a logic programming framework is most effective for knowledge processing. In the first step, we would show that application programs and the operating system (PIMOS), that are all written in KL1¹, can work efficiently on a KL1 engine. The PIM hardware, the firmware, and KL1 language processor make the KL1 engine. My presentation reports the current status of the development of the KL1 engine.

When starting the PIM development, we did not have enough experience to select one of several alternative PIM architectures which can give the best performance for executing KL1 programs. Thus, the purpose of the development of more than one PIM was to examine and compare the technical issues for different architectures. First, the machine architectures and the features of each PIM are presented. Then, the implementation of the KL1 engine on the PIMs is reviewed. Next, the current status of the development of the hardware is reported. Last, how each module of the firmware works to execute KL1 programs is described. Then, the progress report on the firmware is made.

## 2 Comparison of Five PIMs

Five PIMs are now being manufactured; PIM/p, PIM/c, PIM/m, PIM/i, and PIM/k. We will compare the specifications of these PIMs to each other with respect to the factors listed below. The following four tables show the comparison (Tables 1, 2, 3 and 4). The technical factors which are concerned with the PIM architectures are:

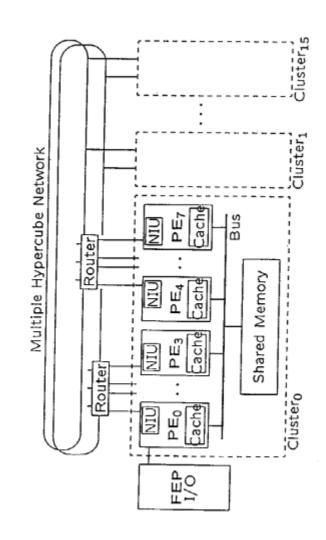

## intra-cluster configuration

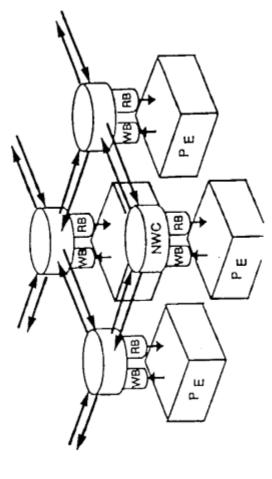

We classify the PIMs with respect to the configuration within a cluster (Tab. 1). Here, a cluster is part of the machine structure, and consists of 10 or so processing elements and a shared memory connected by a bus. In PIM/p, every four NIs are connected to a router, which works as a node in a global network.

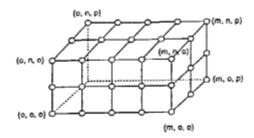

## · inter-cluster configuration

There are many possible methods and topologies of the networks which connect the clusters to each other: bus, hypercube, crossbar, mesh, omega, tree, and so on (Tab. 2).

<sup>&</sup>lt;sup>1</sup>KL1 is a concurrent logic programming language and was developed in ICOT.

Table 1: Intra-cluster Configuration

|       | Number of PEs | Number of NIs | Comment                  |

|-------|---------------|---------------|--------------------------|

| PIM/p | 8             | 8             | each PE has NI           |

| PIM/c | 8             | 1             | NI is connected to a bus |

| PIM/m | 1             | 1             |                          |

| PIM/i | 8             | 1             | NI is connected to a bus |

| PIM/k | 16            | 1             | one of 16 PEs has NI     |

(PE = processing element, NI = network interface)

Table 2: Inter-cluster Configuration

|       | Topology  | Number of Clusters | Total number of PEs |

|-------|-----------|--------------------|---------------------|

| PIM/p | hypercube | 64                 | 512                 |

| PIM/c | crossbar  | 32                 | 256                 |

| PIM/m | mesh      | -                  | 256                 |

| PIM/i | -         | 2                  | 16                  |

| PIM/k | -         | 2                  | 32                  |

Notice that the PIM/m architecture does not include a part named "cluster" in fact. In the table 1, one PE with a NI is regarded as a cluster for comparison. Actually, each PE of PIM/m has its own private memory and there is no shared memory over the entire machine.

- KL1-oriented instruction set and processor configuration (Tab. 3)

Whether a processor is a RISC or a CISC is one of major concerns. If a processor is a RISC, its compiler must generate efficient machine codes in particular. In case of a CISC, we have to support micro programming. With respect to its architecture, a tag architecture may make a symbolic manipulation efficient.

- coherent cache

An architecture which can exploit the data locality is possibly effective to the KL1

Table 3: Specification on Processing Element

|       | Instruction set           | Cycle time | LSI fabrication | Line interval |

|-------|---------------------------|------------|-----------------|---------------|

| PIM/p | RISC + macro instruction  | 60 ns      | standard-cell   | 0.96 μm       |

| PIM/c | CISC (micro programmable) | 50 ns      | gatearrays      | 0.8 µm        |

| PIM/m | CISC (micro programmable) | 60 ns      | standard-cell   | 0.8 μm        |

| PIM/i | RISC                      | 100 ns     | standard-cell   | 1.2 μm        |

| PIM/k | RISC                      | 100 ns     | custom          | 1.2 μm        |

Table 4: Specification on Coherent Cache

|       | Protocol                                         | Number of states |

|-------|--------------------------------------------------|------------------|

| PIM/p | invalidation (Illinois)                          | 4                |

| PIM/c | invalidation (modified Illinois)                 | 5                |

| PIM/m |                                                  | -                |

| PIM/i | broadcasting                                     | 6                |

| PIM/k | invalidation (modified Berkeley)<br>hierarchical | 4                |

execution. So, we suppose an architecture which can keep the locality high; there are ten processing elements, which are connected to a shared memory through coherent caches and a bus. The coherent caches is necessary to decrease the bus traffic. All of the PIMs adopt the write-back coherent cache method (Tab. 4).

Notice that PIM/k has the hierarchical cache; a PE of PIM/k has its first cache, the four PEs share a second cache, and the four second caches share a global memory.

## I/O channel

Input and output to storage devices make the PIMs more practical. We have the two extremes; each processor has its own I/O channel, and an entire system has one I/O channel. The former configuration can obtain more disk throughput but the amount of the hardware increases and the control is more difficult.

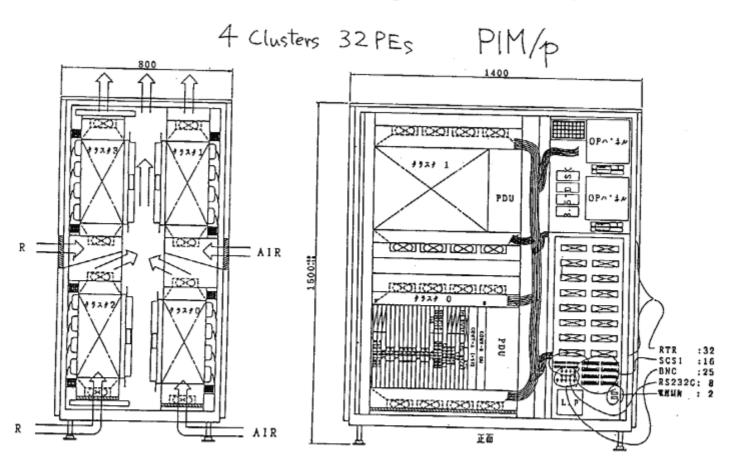

A plan of how much disk capacity the PIM experimental versions provide is as follows. A cluster of PIM/p (8 PEs) has two SCSI channels and 2.32GB disks totally. In PIM/m, every 8 PEs have a SCSI channel and a 600MB disk.

## 3 Current Status on Hardware Development

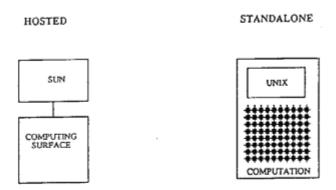

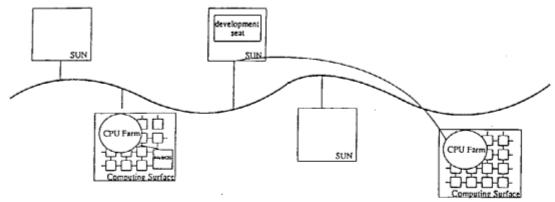

We report the current status concerned with the PIM/p hardware. Currently we are assembling the experimental version and are checking the operations on the hardware level. The next refined version of this experimental one which consists of 1 clusters (8 PEs) will first start working at ICOT in March of 1991. We hope that PIMOS on PIM/p (128 PEs) will start running in the latter half of that year.

As for the production model of PIM/m, two sets of 16PE system will arrive at ICOT in April of 1991. We hope that PIMOS on PIM/m (256 PEs) will be able to run before the end of that year.

The experimental systems of PIM/c, PIM/i and PIM/k are now being fabricated by each manufacturer.

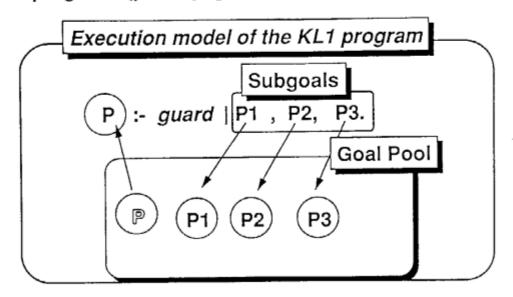

## 4 How to Implement KL1 Engine on PIMs

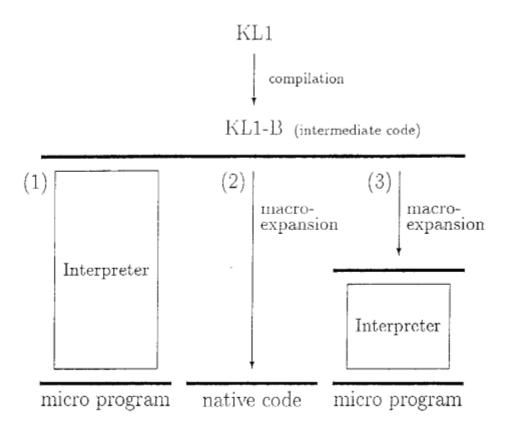

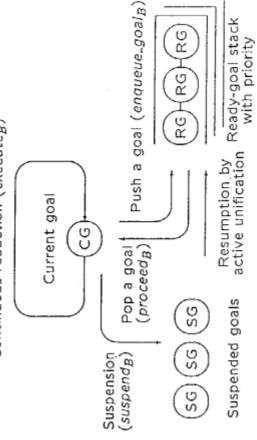

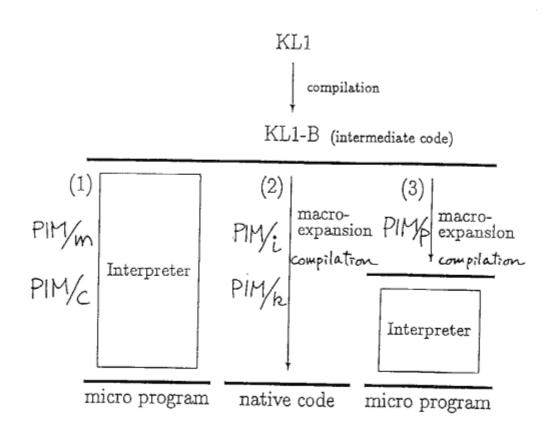

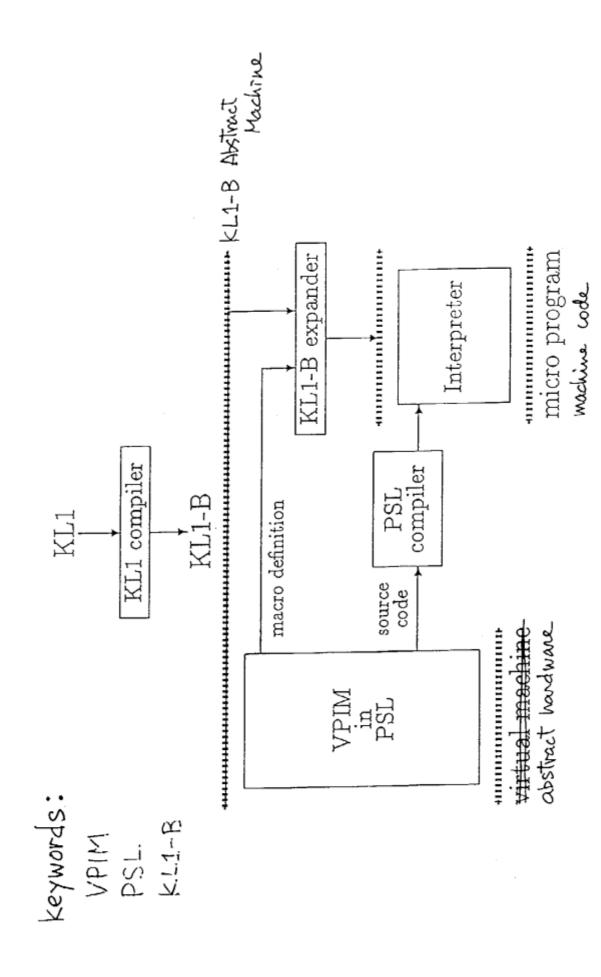

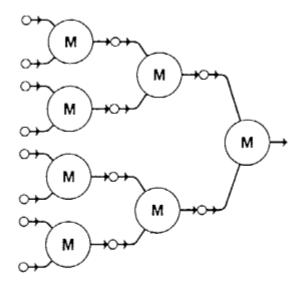

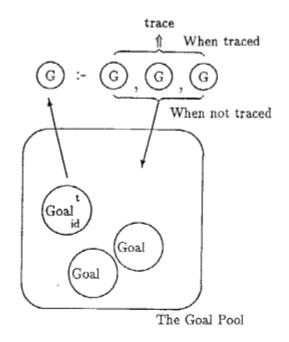

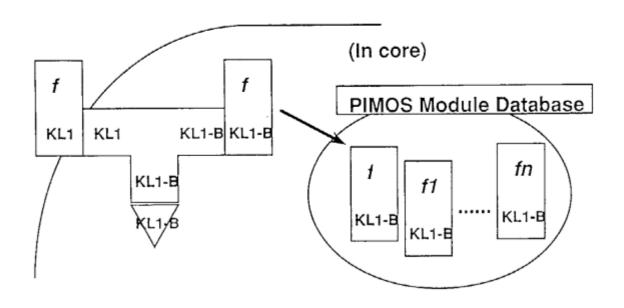

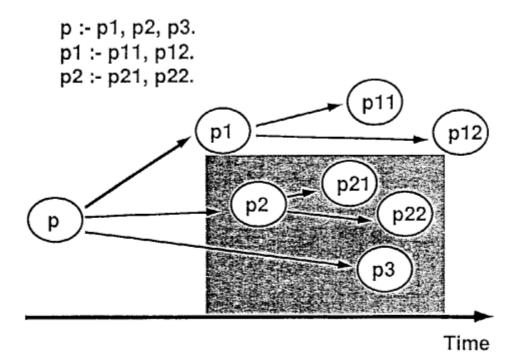

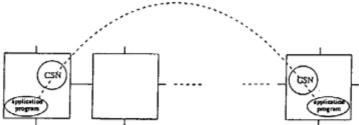

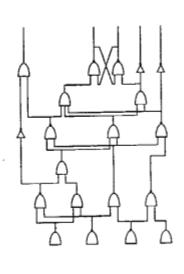

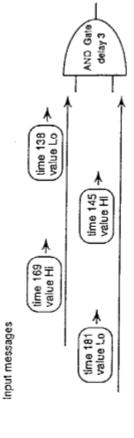

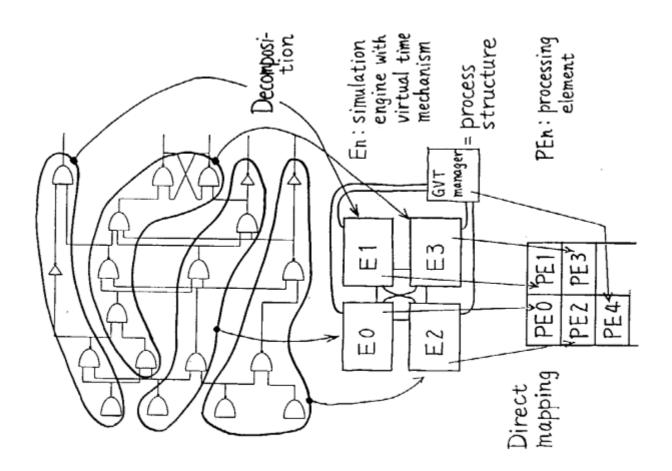

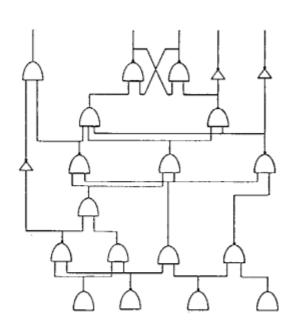

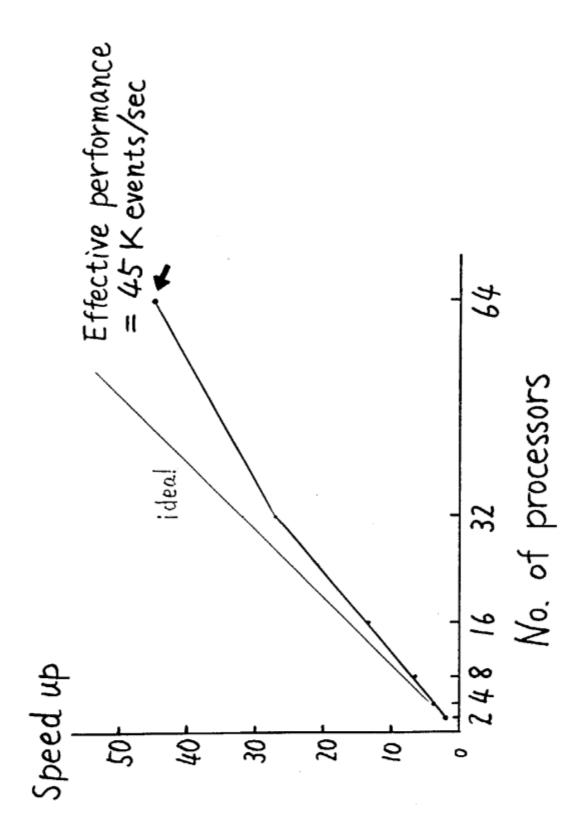

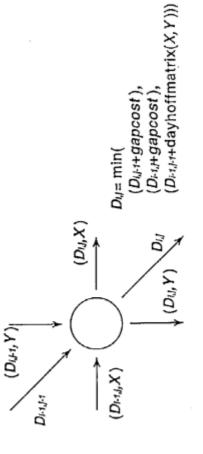

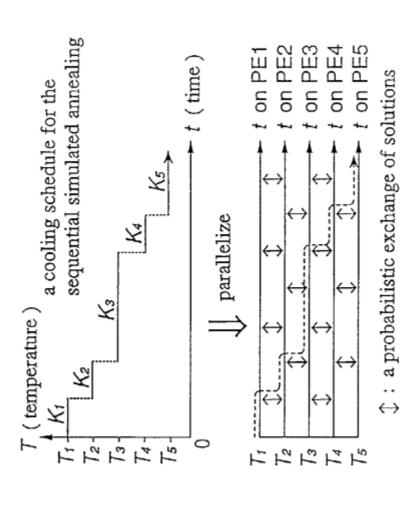

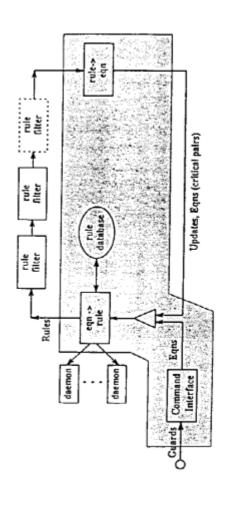

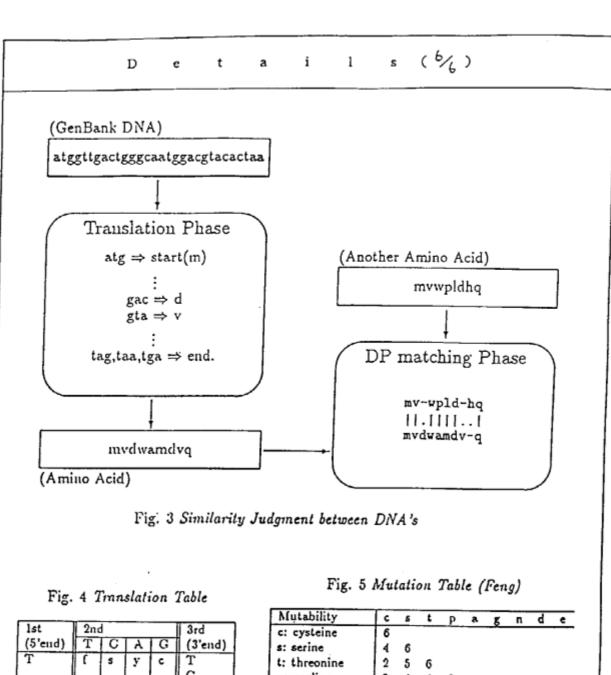

In this section, we describe how to compile KL1 programs into the PIM machine codes. First, a KL1 program is compiled into an intermediate code, KL1-B, which corresponds to the WAM instruction of Prolog. Here, we have three execution methods (Fig. 1). The first

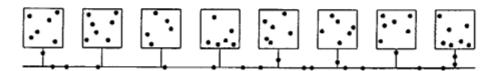

Figure 1: Three Methods for Executing KL1-B Instructions

method (Fig. 1 (1)) is to interpret the KL1-B codes directly as a high-level machine language by using a micro programming technique. Method (2) is to macro-expand (or compile) the KL1-B instructions into native codes <sup>2</sup>. After that, the native codes are linked with run-time libraries and, then, can be executed. Method (1) is suitable for PIM/m and PIM/c, and (2) for PIM/i and PIM/k. Method (3) is located in the middle position; a KL1-B instruction is further macro-expanded (or compiled) to yet another intermediate codes lower than KL1-B. PIM/p adopts a mixed way of these three methods (1), (2) and (3).

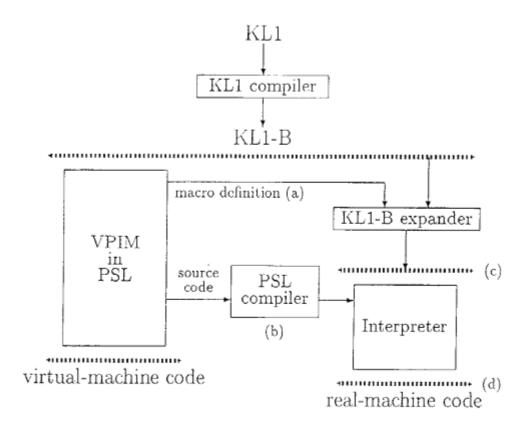

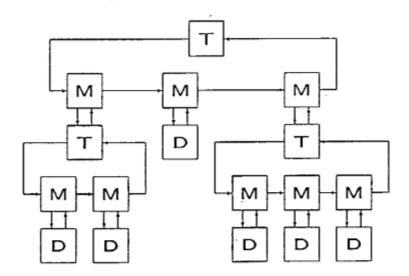

Next we show the organization of software modules of the KL1 engine (Fig. 2). To write the firmware for the five PIMs efficiently and commonly as possible, we introduce a virtual PIM hardware which is an abstraction of the five PIMs, and design a language for describing the firmware on the virtual hardware. We call the firmware VPIM (Virtual PIM) and the language PSL (PIM System Descriptive Language). VPIM is an abstract machine for KL1-B. PSL is an extension of the C language. Statements of PSL can be source codes to be compiled and, in the same form, macro-definitions as well. Thus, the KL1-B expander does macro-expansion of KL1-B instructions with regarding VPIM (firmware in PSL) as the macro-definitions (Fig. 2 (a)). Actually, some KL1-B instructions are fully macro-expanded or compiled, and others are macro-expanded down to another intermediate level lower than KL1-B (Fig. 2 (c)). Depending on each PIM architecture, we have to find out the appropriate intermediate level and to use the KL1-B expander and the PSL compiler properly. On the other hand, the PSL compiler compiles the VPIM source codes (not macro-expanded) to the real-machine codes for the KL1-B interpreter (Fig. 2 (b)). In detail, a

<sup>&</sup>lt;sup>2</sup>Indeed, the language KL1-B is designed so that the macro-expansion of KL1-B codes generates a sequence of machine codes.

Figure 2: KL1 Language Processors

segment of VPIM codes corresponding to the intermediate-level instructions (c) is compiled to the native codes for the virtual PIM hardware once. The native codes of the virtual hardware can be translated to real-machine codes with little effort (Fig. 2 (d)).

Furthermore, VPIM has a useful feature; VPIM itself can be compiled as a C program with slight modification. Thus, we can easily prove the correctness of VPIM on conventional computers (the SUN workstation, Sequent Symmetry, and so on).

Actually, in order to implement the KL1-B expander easily, the part of VPIM which corresponds to macro-definition for the KL1-B expander is written in KL1, not in PSL. Thus, the KL1-B expander can be used as a self-expander also.

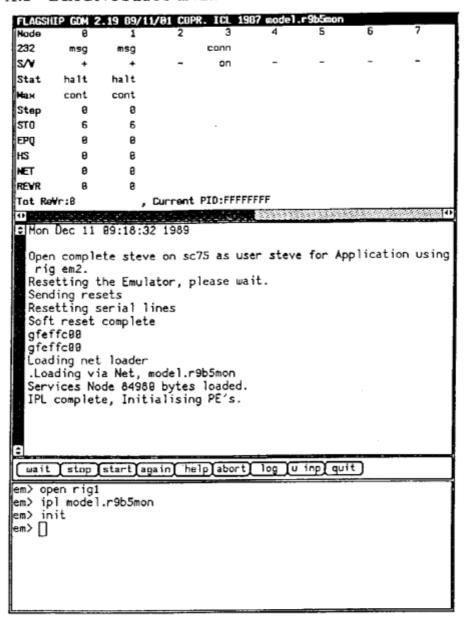

## 5 Current Status on Software Development

We show the current status on the PIM software development as follows.

- VPIM: Now we have just released version 0.5, which does not only implements almost

all the basic intra-cluster functions (goal reduction, goal management, garbage collection, and so on) but also includes the following new features: packetized inter-cluster

communication, and distributed resource management. Version 1.0 will be released in

Dec. of this year which will include the SCSI device driver.

- KL1 compiler, PSL compiler and KL1-B expander: Prototyping of these compilers and expander is almost finished. These compilers can be used as self-compilers on the real PIM hardware as well. Their performance will be improved.

Miscellaneous: Bootstrap routines and software for service processors are being developed. The bootstrap routines include the system initializer, IPL, and so on. The software for service processors includes debuggers, tracers, and statistic measurers.

The compiled code of the append program can run on a PIM/p hardware simulator, actually. Thus, our linker and loader work well, too.

## 6 Concluding Remarks

Our future plan is as follows: assembling and testing the machine hardware, and improving performance of the KL1 engines. We also would like to explore the possibility of other methods for efficient KL1 parallel implementation.

## Acknowledgement:

We would like to thank the researchers who have been working on the PIMs and the Multi-PSI.

## References

[Goto 89a] A. Goto: Research and Development of the Parallel Inference Machine in the FGCS Project, In Parallel Processing and Artificial Intelligence, Eds. M. Reeve and S. E. Zenith, pp.65-96, John Wiley & Sons (1989).

[Goto 89b] A. Goto: Developing the Parallel Inference Machine, In Proc. of Joint Japanese-American Workshop on Future Trends in Logic Programming, ANL-89/43, Argonne National Laboratory, pp.51-55 (Oct. 1989).

# PIM Architectures and R&D Status

Keiji Hirata (ICOT)

## Outline

- Machine Architectures and their Features Five PIMs

- 2. Current Status on Hardware Development

- Software Cofiguration

Firmware and Language Tools

- 4. Current Status on Software Development

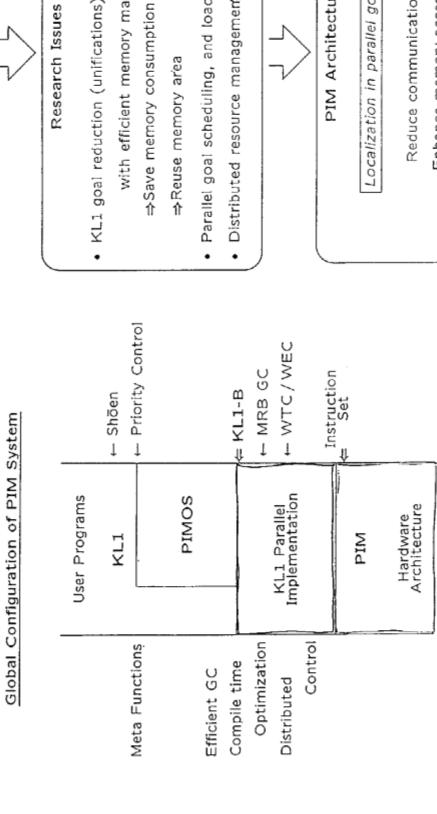

- with efficient memory management KL1 goal reduction (unifications) ⇒Save memory consumption

- · Parallel goal scheduling, and load distribution

- Distributed resource management

## PIM Architecture

## Localization in parallel goal reduction

Enhance memory access locality Reduce communication traffic

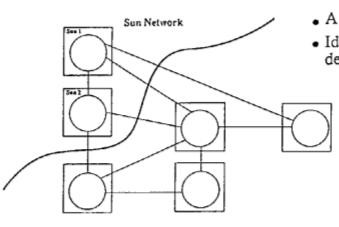

shared variable PE ЬΕ Network  $\bigcirc$ Parallel KL1 Goals in PIM (0) ЬE РЕ stream Ó (<u>©</u> ⇒ (5) (G ЪЕ ЬE stream Cluster Cluster ÞΕ ЬΕ (Ó (<u>0</u> (PE) Shared Memory (PE) .... Cluster Abstract Configuration of PIM (PE) Network (PE) Shared Memory (PE) ... Cluster (PE)

# Alternatives in KL1-B Implementation

KL1-B: Abstract machine instruction for KL1

- KL1-B interpretation by microprogram (HLIC/CISC).

- → Dispatching overheads to micro-instructions.

- (2)Expanded compiled code in RISC-like instruction set.

- → Code fetch overheads

- (3)

Small subroutines in RISC-like instructions for each KL1-B instruction.

- → Overheads in subroutine call and return.

- → Overheads in parameter passsing.

with Conditional Macro-call instructions RISC-like instruction set RISC + HLIC/CISC →

+ macro-body in local memory + indirect registers

Incremental garbage collection by MRB.

Non-busy waiting goal scheduling.

Goal reduction by register.

Three Methods For Executing KL1-B Instructions

PIM/p

Fujitsu

PIM/m

Mitsubishi

PIM/c

Hitachi

PIM/

Oki

PIM/b Toshiba

## Global Configuration of the PIM/p

- Cluster: 8 PEs + shared memory

- 16 clusters connected by multiple hyper-cube network

( <del>128</del> PEs in total ) 512

## PIM/p Hardware Architecture

- Machine instruction set for KL1

- ⇒ Short machine cycle by 4 stage pipeline (Hopefully 1 instruction / 50nsec cycle)

- ⇒ Direct support for MRB GC and free list

- ⇒ Conditional macro-call instructions

- Coherent local cache for KL1

- ⇒ Efficient communication within a cluster

- ⇒ Low cost hardware lock

- High performance inter-cluster network

- ⇒ Efficient both for short and long messages

- ⇒ A network port on each PE to send and receive messages where required

## PIM/p Global Specification

Processing Elements

| One cycle pipeline by 4 stages. |

|---------------------------------|

| 40 bit × 32 W                   |

| 50 bit x 8 K W                  |

|                                 |

| 64 KB                           |

| 256 column, 4 set, 32 B/block,  |

| 2 block/sector                  |

| Write back, Invalidation,       |

| Special commands for KL1        |

|                                 |

Cluster

| Number of PE  | 8      |

|---------------|--------|

| Shared Memory | 256 MB |

Network

| Topology   | Doubled Hyper-cube (Max 6 dimension)                   |

|------------|--------------------------------------------------------|

| Throughput | Max 20 MB/sec in each link<br>( 40 MB/sec for cluster) |

## Inter-cluster Configuration

|       | Topology  | Number of Clusters | Total number of PEs |

|-------|-----------|--------------------|---------------------|

| PIM/p | hypercube | 64                 | 512                 |

| PIM/c | crossbar  | 32                 | 256                 |

| PIM/m | mesh      | -                  | 256                 |

| PIM/i |           | 2                  | 16                  |

| PIM/k |           | 2                  | 32                  |

## Intra-cluster Configuration

|       | Number of PEs | Number of NIs | Comment                    |

|-------|---------------|---------------|----------------------------|

| PIM/p | 8             | 8             | each PE has NI             |

| PIM/c | 8             | 1             | NI is connected to the bus |

| PIM/m | 1             | 1             |                            |

| PIM/i | 8             | 1             | NI is connected to the bus |

| PIM/k | 16            | 1             | one of 16 PEs has NI       |

(PE = processing element, NI = network interface)

## Specification on Processing Element

|       | Instruction set           | Cycle time | LSI fabrication device | Line interval |

|-------|---------------------------|------------|------------------------|---------------|

| PIM/p | RISC + macro instruction  | 60 ns      | standard cells         | 0.96 μm       |

| PIM/c | CISC (micro programmable) | 50 ns      | gate arrays            | 0.8 μm        |

| PIM/m | CISC (micro programmable) | 60 ns      | cell base              | 0.8 μm        |

| PIM/i | RISC                      | 100 ns     | standard cells         | 1.2 μm        |

| PIM/k | RISC                      | · 100 ns   | custom cells           | 1.2 μm        |

## Specification on Coherent Cache

|       | Protocol                                       | Number of states |

|-------|------------------------------------------------|------------------|

| PIM/p | invalidation (Illinois)                        | 4                |

| PIM/c | invalidation (modified Illinois)               | 5                |

| PIM/m |                                                |                  |

| PIM/i | broadcasting                                   | 6                |

| PIM/k | invalidation (modified Berkeley), hierarchical | 4                |

Specification on Disk Channel

|       | Number of PEs / Channel | GB / Channel |

|-------|-------------------------|--------------|

| PIM/p | 4                       | 1.160        |

| PIM/c | 1                       | -            |

| PIM/m | 8                       | 0.6          |

| PIM/i | 8                       | -            |

| PIM/k | · 1                     |              |

## PIM Arrival Schedule

(as of Oct. '90)

VPIM (Virtual PIM)

implementing KL1-B engine

firmware on virtual PIM hardware

implementation techniques of MultiPSI V2

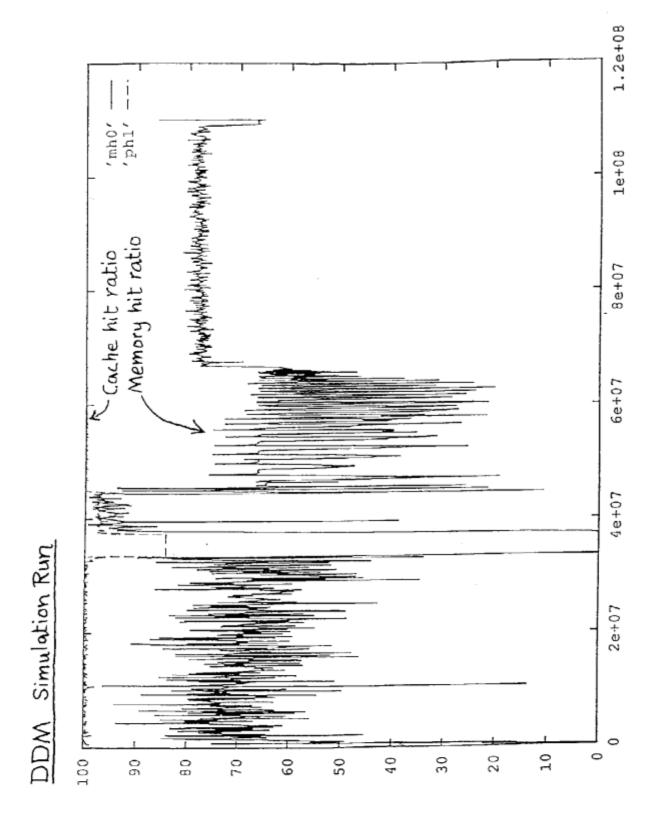

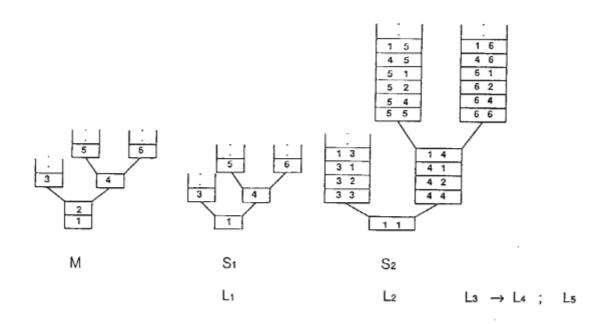

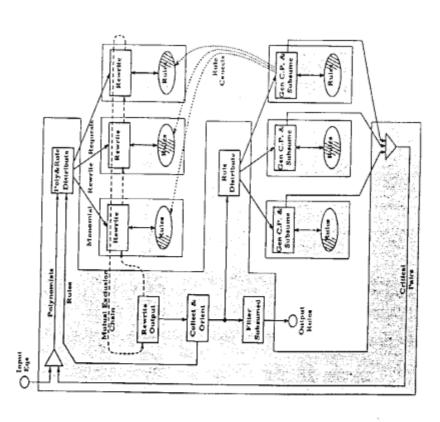

written in PSL (PIM Descriptive Language)